## A Generalized Processor Mapping Technique for Array Redistribution

Ching-Hsien Hsu, Yeh-Ching Chung, *Member*, *IEEE Computer Society*, Don-Lin Yang, *Member*, *IEEE Computer Society*, and Chyi-Ren Dow

Abstract—In many scientific applications, array redistribution is usually required to enhance data locality and reduce remote memory access in many parallel programs on distributed memory multicomputers. Since the redistribution is performed at runtime, there is a performance trade-off between the efficiency of the new data decomposition for a subsequent phase of an algorithm and the cost of redistributing data among processors. In this paper, we present a generalized processor mapping technique to minimize the amount of data exchange for BLOCK-CYCLIC(kr) to BLOCK-CYCLIC(r) array redistribution and vice versa. The main idea of the generalized processor mapping technique is first to develop mapping functions for computing a new rank of each destination processor. Based on the mapping functions, a new logical sequence of destination processors can be derived. The new logical processor sequence is then used to minimize the amount of data exchange in a redistribution. The generalized processor mapping technique can handle array redistribution with arbitrary source and destination processor sets and can be applied to multidimensional array redistribution. We present a theoretical model to analyze the performance improvement of the generalized processor mapping technique. To evaluate the performance of the proposed technique, we have implemented the generalized processor mapping technique on an IBM SP2 parallel machine. The experimental results show that the generalized processor mapping technique can provide performance improvement over a wide range of redistribution problems.

Index Terms—Array redistribution, generalized processor mapping, distributed memory multicomputers, runtime support.

#### 1 Introduction

The data parallel programming model has become a widely accepted paradigm for programming distributed memory multicomputers. To efficiently execute a data parallel program on a distributed memory multicomputer, appropriate data decomposition is critical. The data decomposition involves data distribution and data alignment. The data distribution deals with how data arrays should be distributed. The data alignment deals with how data arrays should be aligned with respect to one another. The purpose of data decomposition is to balance the computational load and minimize the communication overheads.

Many data parallel programming languages, such as High Performance Fortran (HPF) [9], Fortran D [6], Vienna Fortran [33], and High Performance C (HPC) [28], provide compiler directives for programmers to specify array distribution. The array distribution provided by those languages, in general, can be classified into two categories, regular and irregular. The regular array distribution, in general, has three types, BLOCK, CYCLIC, and BLOCK-CYCLIC(c). The irregular array distribution uses user-defined array distribution functions to specify array distribution.

In some algorithms, such as multidimensional fast Fourier transform [29], the Alternative Direction Implicit (ADI)

• The authors are with the Department of Information Engineering, Feng Chia University, Taichung, Taiwan 407, ROC. E-mail: chhsu@plum.iecs.fcu.edu.tw, {ychung, dlyang, crdow}@fcu.edu.tw.

Manuscript received 29 Jan. 1999; revised 6 Sept. 2000; accepted 22 Jan. 2001. For information on obtaining reprints of this article, please send e-mail to: tpds@computer.org, and reference IEEECS Log Number 109077.

method for solving two-dimensional diffusion equations, and linear algebra solvers [21], an array distribution that is well suited for one phase may not be good for a subsequent phase in terms of performance. Array redistribution is required for those algorithms at runtime. Therefore, many data parallel programming languages support runtime primitives for changing a program's array decomposition [1], [2], [9], [28], [33]. Since array redistribution is performed at runtime, there is a performance trade-off between the efficiency of a new data decomposition for a subsequent phase of an algorithm and the cost of redistributing arrays among processors. Thus, efficient methods for performing array redistribution are of great importance for the development of distributed memory compilers for those languages.

In this paper, we present a generalized processor mapping technique to minimize the amount of data exchange of BLOCK-CYCLIC(kr) to BLOCK-CYCLIC(r)redistribution and vice versa. The data transmission cost of a redistribution can be reduced. Compared with the technique proposed by Kalns et al. [12], the generalized processor mapping technique is effective not only on BLOCK to BLOCK-CYCLIC(r) (or vice versa) redistribution but also on BLOCK-CYCLIC(kr) to BLOCK-CYCLIC(r) and BLOCK-CYCLIC(r) to BLOCK-CYCLIC(kr) array redistribution. Another contribution of the generalized processor mapping technique is the ability to handle array redistribution with arbitrary source and destination processor sets. We also present a theoretical model to compute the amount of data that is retained locally and to analyze the performance improvement through a redistribution. The generalized processor mapping technique has the following characteristics:

- The generalized processor mapping technique can minimize the amount of data that needs to be communicated in BLOCK-CYCLIC(kr) to BLOCK-CYCLIC(r) and BLOCK-CYCLIC(r) to BLOCK-CYCLIC(kr) array redistribution. The data transmission cost of a redistribution can be reduced.

- The generalized processor mapping technique can handle array redistribution with arbitrary source and destination processor sets and also multidimensional arrays.

- The proposed mapping functions determine a unique logical processor sequence that achieves the maximum amount of data retained locally in a redistribution.

- If the source processor set and destination processor set of a redistribution are two disjoint sets, then the generalized processor mapping technique will be stultified.

We have implemented the generalized processor mapping technique on an IBM SP2 parallel machine. The experimental results show that the generalized processor mapping technique provides performance improvement for most redistribution samples.

The rest of this paper is organized as follows: In Section 2, a brief survey of related work will be presented. In Section 3, we will introduce notations and terminology used in this paper. Section 4 presents the generalized processor mapping technique for BLOCK-CYCLIC(r) to BLOCK-CYCLIC(r) and BLOCK-CYCLIC(r) to BLOCK-CYCLIC(r) redistribution. In Section 5, we will present the generalized processor mapping technique for multidimensional array redistribution. The performance analysis and experimental results will be given in Section 6.

#### 2 RELATED WORK

Many methods for performing array redistribution have been presented in the literature. These techniques can be classified into multicomputer compiler techniques [27] and runtime support techniques. We briefly describe the related research in these two approaches.

Gupta et al. [7] derived closed form expressions to efficiently determine the send/receive processor/data sets. They also provided a virtual processor approach [8] for addressing the problem of reference index-set identification for array statements with BLOCK-CYCLIC(c) distribution and formulated active processor sets as closed forms. A recent work in [16] extended the virtual processor approach to address the problem of memory allocation and index-set identification. By using their method, closed form expressions for index-sets of arrays that were mapped to processors using one-level mapping can be translated to closed form expressions for index-sets of arrays that were mapped to processors using two-level mapping and vice versa. A similar approach that addressed the problems of the index set and the communication sets identification for array statements with BLOCK-CYCLIC(c) distribution was presented in [24]. In [24], the BLOCK-CYCLIC(k) distribution was viewed as a union of k CYCLIC distribution. Since the communication sets for CYCLIC distribution is easy to

determine, communication sets for BLOCK-CYCLIC(k) distribution can be generated in terms of unions and intersections of some CYCLIC distributions.

In [3], Chatterjee et al. enumerated the local memory access sequence of communication sets for array statements with BLOCK-CYCLIC(c) distribution based on a finite-state machine. In this approach, the local memory access sequence can be characterized by an FSM at most c states. In [17], Kennedy et al. also presented algorithms to compute the local memory access sequence for array statements with BLOCK-CYCLIC(c) distribution. Lee and Chen [18] derived communication sets for statements of arrays which were distributed in arbitrary BLOCK-CYCLIC(c) fashion. They also presented closed form expressions of communication sets for restricted block size. In [4], we proposed a basiccycle calculation to efficiently generate the communication sets for array redistribution. The greatest advantage of this method is the ability of fast indexing. In [11], we proposed efficient algorithms for BLOCK-CYCLIC(kr) to BLOCK-CYCLIC(r) and BLOCK-CYCLIC(r) to BLOCK-CYCLIC(kr)redistribution. The most significant improvement of the algorithms is that a processor does not need to construct the send/receive data sets for a redistribution.

Thakur et al. [25], [26] presented algorithms for runtime array redistribution in HPF programs. For BLOCK-CYCLIC(kr) to BLOCK-CYCLIC(r) redistribution (or vice versa), in most cases, a processor scanned its local array elements once to determine the destination (source) processor for each block of array elements of size r in the local array. In [10], an approach for generating communication sets by computing the intersections of index sets corresponding to the LHS and RHS of array statements was presented. The intersections are computed by a scanning approach that exploits the repetitive pattern of the intersection of two index sets. In [22], [23], Ramaswamy and Banerjee used a mathematical representation, PITFALLS, for regular data redistribution. The basic idea of PITFALLS is to find all intersections between source and destination distributions. Based on the intersections, the send/receive processor/data sets can be determined and general redistribution algorithms can be devised. Prylli and Touranchean [21] proposed a runtime scan algorithm for BLOCK-CYCLIC array redistribution. Their approach has the same time complexity as that proposed in [23] but has a simple basic operation compared to that proposed in [23]. The disadvantage of these approaches is that, when the number of processors is large, iterations of the outermost loop in intersection algorithms increases as well. This leads to high indexing overheads and degrades the performance of a redistribution algorithm.

The above researches focus on efficient generation of communication sets. For the communication part, a spiral mapping technique [32] was proposed. The main idea of this approach was to map formal processors onto actual processors such that the global communication can be translated to the local communication in a certain processor group. Since the communication is local to a processor group, one can reduce communication conflicts when performing a redistribution. Kalns and Ni [12], [13] proposed a processor mapping technique to minimize the

amount of data exchange for BLOCK to BLOCK-CYCLIC(r) redistribution and vice versa. Using the data to logical processor mapping, they show that the technique can achieve the maximum ratio between data retained locally and the total amount of data exchanged. Walker and Otto [30] used the standardized Message Passing Interface (MPI) to express the redistribution operations. They implemented the BLOCK-CYCLIC array redistribution algorithms in a synchronous and an asynchronous scheme. Since the excessive synchronization overheads occurred from the synchronous scheme, they also presented the random and optimal scheduling algorithms for BLOCK-CYCLIC array redistribution.

Kaushik et al. [14], [15] proposed a multiphase redistribution approach for BLOCK-CYCLIC(s) to BLOCK-CYCLIC(t) redistribution. The main idea of multiphase redistribution is to perform a redistribution as a sequence of redistributions such that the communication cost of data movement among processors in the sequence is less than that of direct redistribution. Instead of redistributing the entry array at one time, a strip mining approach was presented in [31]. In this approach, portions of array elements were redistributed in sequence in order to overlap the communication and computation. In [19], a generalized circulant matrix formalism was proposed to reduce the communication overheads for BLOCK-CYCLIC(r) to BLOCK-CYCLIC(kr) redistribution. Using the generalized circulant matrix formalism, the authors derived direct, indirect, and hybrid communication schedules for the cyclic redistribution with the block size changed by an integer factor k. They also extended this technique to solve some multidimensional redistribution problems [20]. However, as the array size increased, the above methods will have a large amount of extra transmission costs and degrades the performance of a redistribution algorithm.

#### 3 PRELIMINARIES

In general, a BLOCK-CYCLIC(s) over P processors to BLOCK-CYCLIC(t) over Q processors redistribution can be classified as one of three types:

- 1. s is divisible by t, i.e., BLOCK-CYCLIC(s=kr) to BLOCK-CYCLIC(t=r) redistribution,

- 2. t is divisible by s, i.e., BLOCK-CYCLIC(s=r) to BLOCK-CYCLIC(t=kr) redistribution, and

- 3. s is not divisible by t and t is not divisible by s.

To simplify the presentation, we use  $kr_{(P)} \rightarrow r_{(Q)}$ ,  $r_{(P)} \rightarrow kr_{(Q)}$ , and  $s_{(P)} \rightarrow t_{(Q)}$  to represent the first, the second, and the third types of redistribution, respectively, for the rest of the paper. In this section, we first present the terminology used in this paper.

**Definition 1.** Given a BLOCK-CYCLIC(s) to BLOCK-CYCLIC(t) redistribution, BLOCK-CYCLIC(s), BLOCK-CYCLIC(t), s, and t are called the source distribution, the destination distribution, the source distribution factor, and the destination distribution factor of the redistribution, respectively.

**Definition 2.** Given an  $s_{(P)} \to t_{(Q)}$ , the source local array of processor  $P_i$ , denoted by  $SLA_i[0:N/P-1]$ , is defined as the set of array elements that are distributed to processor  $P_i$  in the

source distribution, where  $0 \le i \le P-1$ . The destination local array of processor  $Q_j$ , denoted by  $DLA_j[0:N/Q-1]$ , is defined as the set of array elements that are distributed to processor  $Q_j$  in the destination distribution, where  $0 \le j \le Q-1$ .

**Definition 3.** Given an  $s_{(P)} \to t_{(Q)}$  redistribution on A[1:N], the source processor of an array element in A[1:N] or  $DLA_j[0:N/Q-1]$  is defined as the processor that owns the array element in the source distribution, where  $0 \le j \le Q-1$ . The destination processor of an array element in A[1:N] or  $SLA_i[0:N/P-1]$  is defined as the processor that owns the array element in the destination distribution, where  $0 \le i \le P-1$ .

**Definition 4.** Given an  $s_{(P)} \to t_{(Q)}$  redistribution on A[1:N], a global complete cycle (GCC) of A[1:N] is defined as  $GCC = lcm(s \times P, t \times Q)$ . We define A[1:GCC] as the first global complete cycle of A[1:N],

$$A[GCC+1:2\times GCC]$$

as the second global complete cycle of A[1:N], and so on.

**Definition 5.** Given an  $s_{(P)} \rightarrow t_{(Q)}$  redistribution on A[1:N], a local complete cycle of a local array is defined as  $LCC_s = GCC/P$  in the source distribution and  $LCC_d = GCC/Q$  in the destination distribution. We define

$$SLA_i[0:LCCs-1](DLA_i[0:LCC_d-1])$$

as the first local complete cycle of

$$SLA_{i}[0:N/P-1](DLA_{i}[0:N/Q-1])$$

and

$$SLA_i[LCC_s: 2 \times LCC_s - 1](DLA_j[LCC_d: 2 \times LCC_d - 1])$$

as the second local complete cycle of

$$SLA_i[0: N/P - 1] (DLA_i[0: N/Q - 1])$$

and so on.

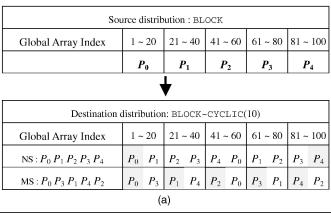

We now give examples to clarify the above definitions. Given a one-dimensional array A[1:100] and P=Q=5 processors, Fig. 1 shows a BLOCK to BLOCK-CYCLIC(10) redistribution on A over five processors. In this paper, we assume that the local array index starts from 0 and the global array index starts from 1. According to Definitions 4 and 5, the size of global complete cycle (GCC) is equal to 100 and the size of the local complete cycle is equal to 20 in both source and destination distributions.

# 4 THE GENERALIZED PROCESSOR MAPPING TECHNIQUE FOR $kr_{(P)} \to r_{(Q)}$ AND $r_{(P)} \to kr_{(Q)}$ ARRAY REDISTRIBUTION

To perform the redistribution shown in Fig. 1, computation as well as communication costs are required in array redistribution. The computation cost consists of the indexing time and the packing/unpacking time. The communication cost includes message startup time and data transmission time. In general, the communication cost

| Source distribution : BLOCK |        |         |         |         |          |  |  |  |  |  |  |  |

|-----------------------------|--------|---------|---------|---------|----------|--|--|--|--|--|--|--|

| Global Array Index          | 1 ~ 20 | 21 ~ 40 | 41 ~ 60 | 61 ~ 80 | 81 ~ 100 |  |  |  |  |  |  |  |

| Local Array Index           | 0 ~ 19 | 0 ~ 19  | 0 ~ 19  | 0 ~ 19  | 0 ~ 19   |  |  |  |  |  |  |  |

| Source Processor            | $P_0$  | $P_1$   | $P_2$   | $P_3$   | $P_4$    |  |  |  |  |  |  |  |

| Destination of                                             | Destination distribution: BLOCK-CYCLIC(10) |              |                  |                    |                    |  |  |  |  |  |  |  |  |

|------------------------------------------------------------|--------------------------------------------|--------------|------------------|--------------------|--------------------|--|--|--|--|--|--|--|--|

| Global Array Index 1 ~ 20 21 ~ 40 41 ~ 60 61 ~ 80 81 ~ 100 |                                            |              |                  |                    |                    |  |  |  |  |  |  |  |  |

| Local Array Index                                          | 0~ 0~                                      | 0~ 0~<br>9 9 | 0 ~ 10 ~<br>9 19 | 10 ~ 10 ~<br>19 19 | 10 ~ 10 ~<br>19 19 |  |  |  |  |  |  |  |  |

| Destination processor                                      | $P_0$ $P_1$                                | $P_2$ $P_3$  | $P_4$ $P_0$      | $P_1$ $P_2$        | $P_3$ $P_4$        |  |  |  |  |  |  |  |  |

Fig. 1. A BLOCK to BLOCK-CYCLIC(10) redistribution on a one-dimensional array A[1:100] over five processors.

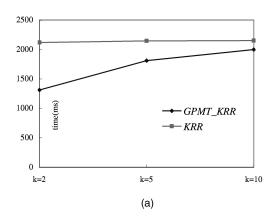

is more expensive in terms of the execution time than the computation cost. Therefore, techniques for reducing communication costs are very important. In [12], a processor mapping technique was proposed to minimize the amount of data exchange in a redistribution. The proposed techniques addressed the case of BLOCK to BLOCK-CYCLIC(x) redistribution. Fig. 2a shows an example of the processor mapping technique for the redistribution shown in Fig. 1. In Fig. 2a, in the destination distribution, the "NS" represents the normal sequence of logical processor ranks that start from 0 to M-1, where M is the number of processors. The "MS" represents the mapping sequence of logical processor ranks that is generated by the mapping function of the processor mapping technique. The shaded portions represent the data that were retained on the same logical processor through the redistribution. In the normal sequence scheme, there are 20 array elements retained locally. However, in the mapping sequence scheme, there are 50 array elements retained locally. Since the global array size is equal to 100, the processor mapping technique provides 30 percent improvement in terms of data transmission time for the redistribution shown in Fig. 1.

We consider another two examples. Fig. 2b and Fig. 2c show the redistribution with different array sizes and destination distribution factors, respectively. In Fig. 2b, a BLOCK to BLOCK-CYCLIC(10) redistribution with larger array size A[1:500] is shown. Both the normal sequence scheme and the mapping sequence scheme have the same amount of array elements retained locally. The processor mapping technique does not provide a larger amount of local data in this case. In Fig. 2c, a BLOCK to BLOCK-CYCLIC(4) redistribution on a one-dimensional array A[1:100] over five processors is shown. Similar to the result of Fig. 2b, the normal sequence and the mapping sequence schemes have the same amount of array elements retained locally. We have the following two observations:

- 1. Given a BLOCK to BLOCK-CYCLIC(r) redistribution with fixed destination distribution factor r, the processor mapping technique is not effective when the array size is larger than the threshold.

- 2. Given a BLOCK to BLOCK-CYCLIC(r) redistribution with fixed array size N, the processor mapping technique is not effective when the destination distribution factor r is smaller than the threshold.

In fact, BLOCK to BLOCK-CYCLIC(r) redistribution (or vice versa) is a special case of  $kr_{(P)} \rightarrow r_{(Q)}$  (or  $r_{(P)} \rightarrow kr_{(Q)}$ ) array redistribution, when  $k=N/P_r$  (or  $k=N/Q_r$ ) where N is the array size. For general redistribution problems, we derive a generalized processor mapping technique for  $kr_{(P)} \rightarrow r_{(Q)}$  (or  $r_{(P)} \rightarrow kr_{(Q)}$ ) array redistribution to minimize the amount of data exchange.

According to the values of  $LCC_s$ ,  $LCC_d$ , and kr,  $kr_{(P)} \rightarrow r_{(Q)}$  and  $r_{(P)} \rightarrow kr_{(Q)}$  array redistributions can be classified into two different types: *optimal type* and *general type*, as shown in Table 1. In the optimal type, the generalized processor mapping technique can derive a mapping sequence such that the amount of data exchange is minimal. In the general type, the generalized processor mapping technique can derive a mapping sequence to reduce the amount of data exchange. We will discuss the generalized processor mapping technique for the optimal type and the general type in Section 4.1 and Section 4.2, respectively.

#### 4.1 The Optimal Type

4.1.1  $kr_{(P)} \rightarrow r_{(Q)}$  Array Redistribution

**A.** P = Q: Based on the characteristics of a redistribution, we have the following lemma:

**Lemma 1.** Given an  $s \to t$  redistribution on A[1:N] over M processors, for a source processor  $P_i$ ,  $SLA_i[m]$ ,  $SLA_i[m+LCC]$ ,  $SLA_i[m+2 \times LCC]$ ,..., and

$$SLA_i[m+N/M \times LCC]$$

| Source distribution: BLOCK |         |           |           |           |           |  |  |  |  |  |  |  |

|----------------------------|---------|-----------|-----------|-----------|-----------|--|--|--|--|--|--|--|

| Global Array Index         | 1 ~ 100 | 101 ~ 200 | 201 ~ 300 | 301 ~ 400 | 401 ~ 500 |  |  |  |  |  |  |  |

|                            | $P_0$   | $P_1$     | $P_2$     | $P_3$     | $P_4$     |  |  |  |  |  |  |  |

|                                                                    | Destination distribution: BLOCK-CYCLIC(10)                                                                                                            |                                                                                                                                                       |                                                                                                                                                       |                                                                                                                                                       |                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |

|--------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|

| Global Array Index 1 ~ 100 101 ~ 200 201 ~ 300 301 ~ 400 401 ~ 500 |                                                                                                                                                       |                                                                                                                                                       |                                                                                                                                                       |                                                                                                                                                       |                                                                                                                                                       |  |  |  |  |  |  |  |  |  |  |

| NS: $P_0 P_1 P_2 P_3 P_4$                                          | p <sub>0</sub> p <sub>1</sub> p <sub>2</sub> p <sub>3</sub> p <sub>4</sub> p <sub>0</sub> p <sub>1</sub> p <sub>2</sub> p <sub>3</sub> p <sub>4</sub> | $p_0 p_1 p_2 p_3 p_4 p_0 p_1 p_2 p_3 p_4$                                                                                                             | p <sub>0</sub> p <sub>1</sub> p <sub>2</sub> p <sub>3</sub> p <sub>4</sub> p <sub>0</sub> p <sub>1</sub> p <sub>2</sub> p <sub>3</sub> p <sub>4</sub> | p <sub>0</sub> p <sub>1</sub> p <sub>2</sub> p <sub>3</sub> p <sub>4</sub> p <sub>0</sub> p <sub>1</sub> p <sub>2</sub> p <sub>3</sub> p <sub>4</sub> | $p_0 p_1 p_2 p_3 p_4 p_0 p_1 p_2 p_3 p_4$                                                                                                             |  |  |  |  |  |  |  |  |  |  |

| MS: $P_0 P_3 P_1 P_4 P_2$                                          | p <sub>0</sub> p <sub>3</sub> p <sub>1</sub> p <sub>4</sub> p <sub>2</sub> p <sub>0</sub> p <sub>3</sub> p <sub>1</sub> p <sub>4</sub> p <sub>2</sub> | p <sub>0</sub> p <sub>3</sub> p <sub>1</sub> p <sub>4</sub> p <sub>2</sub> p <sub>0</sub> p <sub>3</sub> p <sub>1</sub> p <sub>4</sub> p <sub>2</sub> | p <sub>0</sub> p <sub>3</sub> p <sub>1</sub> p <sub>4</sub> p <sub>2</sub> p <sub>0</sub> p <sub>3</sub> p <sub>1</sub> p <sub>4</sub> p <sub>2</sub> | p <sub>0</sub> p <sub>3</sub> p <sub>1</sub> p <sub>4</sub> p <sub>2</sub> p <sub>0</sub> p <sub>3</sub> p <sub>1</sub> p <sub>4</sub> p <sub>2</sub> | p <sub>0</sub> p <sub>3</sub> p <sub>1</sub> p <sub>4</sub> p <sub>2</sub> p <sub>0</sub> p <sub>3</sub> p <sub>1</sub> p <sub>4</sub> p <sub>2</sub> |  |  |  |  |  |  |  |  |  |  |

(b)

| Source Distribution: BLOCK |        |         |         |         |          |  |  |  |  |  |  |  |

|----------------------------|--------|---------|---------|---------|----------|--|--|--|--|--|--|--|

| Global Array Index         | 1 ~ 20 | 21 ~ 40 | 41 ~ 60 | 61 ~ 80 | 81 ~ 100 |  |  |  |  |  |  |  |

|                            | $P_0$  | $P_1$   | $P_2$   | $P_3$   | $P_4$    |  |  |  |  |  |  |  |

|                            |        |         |         |         |          |  |  |  |  |  |  |  |

|                                                            | Destination Distribution: BLOCK-CYCLIC(4) |                               |                       |                                                                            |                               |  |  |  |  |  |  |  |  |  |

|------------------------------------------------------------|-------------------------------------------|-------------------------------|-----------------------|----------------------------------------------------------------------------|-------------------------------|--|--|--|--|--|--|--|--|--|

| Global Array Index 1 ~ 20 21 ~ 40 41 ~ 60 61 ~ 80 81 ~ 100 |                                           |                               |                       |                                                                            |                               |  |  |  |  |  |  |  |  |  |

| NS: $P_0 P_1 P_2 P_3 P_4$                                  | $p_0$ $p_1$ $p_2$ $p_3$ $p_4$             | $p_0$ $p_1$ $p_2$ $p_3$ $p_4$ | $p_0 p_1 p_2 p_3 p_4$ | p <sub>0</sub> p <sub>1</sub> p <sub>2</sub> p <sub>3</sub> p <sub>4</sub> | $p_0$ $p_1$ $p_2$ $p_3$ $p_4$ |  |  |  |  |  |  |  |  |  |

| $MS: P_0 P_3 P_1 P_4 P_2$                                  | $p_0$ $p_3$ $p_1$ $p_4$ $p_2$             | $p_0$ $p_3$ $p_1$ $p_4$ $p_2$ | $p_0 p_3 p_1 p_4 p_2$ | p <sub>0</sub> p <sub>3</sub> p <sub>1</sub> p <sub>4</sub> p <sub>2</sub> | $p_0$ $p_3$ $p_1$ $p_4$ $P_2$ |  |  |  |  |  |  |  |  |  |

(c)

Fig. 2. Examples of processor mapping technique for BLOCK to BLOCK-CYCLIC(r) redistribution on A[1:N] over five processors. (a) r=10, N=100. (b) r=10, N=500. (c) r=4, N=100.

have the same destination processor, where  $0 \le i \le M-1$  and  $0 \le m \le LCC-1$ .

**Proof.** In a  $s \to r$  redistribution,  $GCC = M \times lcm(s,t)$  and LCC = lcm(s,t). In the source distribution, for a source processor  $P_i$ , if the global array index of  $SLA_i[m]$  is  $\alpha$ , then the global array indices of  $SLA_i[m+LCC]$ ,  $SLAi[m+2 \times LCC], \ldots$ , and  $SLA_i[m+N/M-LCC]$  are  $\alpha + GCC$ ,  $\alpha + 2 \times GCC, \ldots$ , and  $\alpha + N/M - GCC$ , respectively, where  $0 \le i \le M-1$  and

$$0 < m < LCC - 1$$

.

Since  $GCC = M \times lcm(s,t)$  and LCC = lcm(s,t), in the destination distribution, if  $A[\alpha]$  is distributed to the destination processor  $P_j$ , so are  $A[\alpha + GCC]$ ,

$$A[\alpha + 2 \times GCC], \ldots,$$

and  $A[\alpha+N/M-GCC]$ , where  $0 \le j \le M-1$  and  $1 \le \alpha \le GCC$ .

**Lemma 2.** Given an  $s \to t$  redistribution on A[1:N] over M processors, for a destination processor  $P_j$ ,  $DLA_j[m]$ ,  $DLA_j[m+LCC]$ ,  $DLA_j[m+2 \times LCC]$ ,..., and

$$DLA_i[m + N/M - LCC]$$

TABLE 1 The Optimal and General Types of  $kr_{(P)} o r_{(Q)}$  and  $r_{(P)} o kr_{(Q)}$  Array Redistribution

| Optimal Type                            | General Type                            |

|-----------------------------------------|-----------------------------------------|

| 1. $kr_{(P)} \rightarrow r_{(Q)}$ with  | $1.kr_{(P)} \rightarrow r_{(Q)}$ with   |

| $LCC_s = kr$                            | $LCC_s \neq kr$                         |

| $2. r_{(P)} \rightarrow k r_{(Q)}$ with | $2. r_{(P)} \rightarrow k r_{(Q)}$ with |

| $LCC_d = kr$                            | $LCC_d \neq kr$                         |

have the same source processor, where  $0 \le j \le M-1$  and  $0 \le m \le LCC-1$ .

**Proof.** The proof of this lemma is similar to Lemma 1.

Given a one-dimensional array A[1:100] and M=5 processors, Fig. 3 shows a BLOCK-CYCLIC(10) to BLOCK-CYCLIC(5) redistribution on A over M processors. According to Lemmas 1 and 2, we know that each local complete cycle (LCC) has the same communication patterns. In Fig. 3, for source processor  $P_2$ , array elements  $SLA_2[0:9]$  and  $SLA_2[10:19]$  are in the first and the second LCC, respectively.  $SLA_2[0:9]$  and  $SLA_2[10:19]$  have the same communication patterns. Therefore, for  $kr \to r$  redistribution, a processor only needs to construct the communication sets for its first LCC. Then, it can perform the redistribution. Similarly, to present the generalized processor mapping technique, we only discuss how to derive a mapping sequence in the first LCC.

Given a  $kr \rightarrow r$  redistribution on a one-dimensional array A[1:N] over M processors, we use

$$< P_0, P_1, P_2, \dots, P_{M-1} >$$

and

$$< P_{\alpha(0)}, P_{\alpha(1)}, P_{\alpha(2)}, \dots, P_{\alpha(M-1)} >$$

to represent the normal sequence and the mapping sequence, respectively, where  $\alpha(j)$  represents the new

logical processor rank of  $P_j$ . The main idea of the generalized processor mapping technique is to distribute the global array elements onto destination processors according to the mapping sequence instead of the normal sequence in the destination distribution. For a destination processor  $P_j$ , the new logical processor rank of  $P_j$  can be determined by the following equation:

$$\alpha(j) = (j \mod k) \times \left\lceil \frac{M}{k} \right\rceil + \left\lceil \frac{j}{k} \right\rceil,$$

(1)

where j = 0 to M - 1.

Fig. 4 shows a BLOCK-CYCLIC(10) to BLOCK-CYCLIC(5) redistribution on a one-dimensional array A[1:100] over five processors. There are two kinds of logical processor sequences illustrated in this example. Since the normal sequence of destination processor ranks is  $P_0$ ,  $P_1$ ,  $P_2$ ,  $P_3$ , and  $P_4$ . According to (1), the new ranks of destination processors  $P_0$ ,  $P_1$ ,  $P_2$ ,  $P_3$ , and  $P_4$  are equal to 0, 3, 1, 4, and 2, respectively. Therefore, the mapping sequence of destination processors is  $P_0$ ,  $P_3$ ,  $P_1$ ,  $P_4$ , and  $P_2$ . From Fig. 4, we can see that there are 20 array elements retained locally in a normal sequence scheme while there are 50 array elements retained locally in a mapping sequence scheme. The generalized processor mapping technique provides a larger amount of local data. The following lemma shows that the mapping sequence generated by (1) can achieve the maximum amount of data that was retained on the same logical processor through a redistribution:

**Lemma 3.** Given a  $kr \rightarrow r$  redistribution on a one-dimensional array A[1:N] over M processors, (1) determines a mapping sequence of destination processors to achieve the maximum ratio  $\left\lceil \frac{k}{M} \right\rceil$ : k, between local data and the global array size.

**Proof.** We prove the lemma in two parts: 1) The maximum ratio is  $\left\lceil \frac{k}{M} \right\rceil$ : k. 2) The mapping sequence generated by (1) can achieve the maximum ratio  $\left\lceil \frac{k}{M} \right\rceil$ : k.

1. Given a  $kr \rightarrow r$  redistribution, for a source processor  $P_i$ , where  $0 \le i \le M-1$ : If k < M, then at most r elements are retained on the local array in each local complete cycle. Since there are M local complete cycles in a GCC, the total

|       | Source: BLOCK-CYCLIC(10) |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |

|-------|--------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|

| Index | 0                        | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19  |

| $P_0$ | 1                        | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 51 | 52 | 53 | 54 | 55 | 56 | 57 | 58 | 59 | 60  |

| $P_1$ | 11                       | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19 | 20 | 61 | 62 | 63 | 64 | 65 | 66 | 67 | 68 | 69 | 70  |

| $P_2$ | 21                       | 22 | 23 | 24 | 25 | 26 | 27 | 28 | 29 | 30 | 71 | 72 | 73 | 74 | 75 | 76 | 77 | 78 | 79 | 80  |

| $P_3$ | 31                       | 32 | 33 | 34 | 35 | 36 | 37 | 38 | 39 | 40 | 81 | 82 | 83 | 84 | 85 | 86 | 87 | 88 | 89 | 90  |

| $P_4$ | 41                       | 42 | 43 | 44 | 45 | 46 | 47 | 48 | 49 | 50 | 91 | 92 | 93 | 94 | 95 | 96 | 97 | 98 | 99 | 100 |

|       | Destination: BLOCK-CYCLIC(5) |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |    |     |

|-------|------------------------------|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|

| Index | 0                            | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 | 14 | 15 | 16 | 17 | 18 | 19  |

| $P_0$ | 1                            | 2  | 3  | 4  | 5  | 26 | 27 | 28 | 29 | 30 | 51 | 52 | 53 | 54 | 55 | 76 | 77 | 78 | 79 | 80  |

| $P_1$ | 6                            | 7  | 8  | 9  | 10 | 31 | 32 | 33 | 34 | 35 | 56 | 57 | 58 | 59 | 60 | 81 | 82 | 83 | 84 | 85  |

| $P_2$ | 11                           | 12 | 13 | 14 | 15 | 36 | 37 | 38 | 39 | 40 | 61 | 62 | 63 | 64 | 65 | 86 | 87 | 88 | 89 | 90  |

| $P_3$ | 16                           | 17 | 18 | 19 | 20 | 41 | 42 | 43 | 44 | 45 | 66 | 67 | 68 | 69 | 70 | 91 | 92 | 93 | 94 | 95  |

| $P_4$ | 21                           | 22 | 23 | 24 | 25 | 46 | 47 | 48 | 49 | 50 | 71 | 72 | 73 | 74 | 75 | 96 | 97 | 98 | 99 | 100 |

Fig. 3. Communication patterns of  $SLA_2$  in BLOCK-CYCLIC(10) to BLOCK-CYCLIC(5) redistribution.

| Source Distribution: BLOCK-CYCLIC(10)                                                                                                                 |  |  |  |  |  |  |  |  |  |  |  |  |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|--|--|--|--|--|

| Global Array Index $\begin{vmatrix} 1 & 11 & 21 & 31 & 41 & 51 & 61 & 71 & 81 & 91 & 10 \\ 20 & 30 & 40 & 50 & 60 & 70 & 80 & 90 & 100 \end{vmatrix}$ |  |  |  |  |  |  |  |  |  |  |  |  |  |

| P <sub>0</sub> P <sub>1</sub> P <sub>2</sub> P <sub>3</sub> P <sub>4</sub> P <sub>0</sub> P <sub>1</sub> P <sub>2</sub> P <sub>3</sub> P <sub>4</sub> |  |  |  |  |  |  |  |  |  |  |  |  |  |

| De                                                                       | Destination Distribution: BLOCK-CYCLIC(5) |           |           |           |           |           |           |           |           |           |  |  |  |  |  |

|--------------------------------------------------------------------------|-------------------------------------------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|-----------|--|--|--|--|--|

| Global Array Index $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |                                           |           |           |           |           |           |           |           |           |           |  |  |  |  |  |

| NS: $P_0 P_1 P_2 P_3 P_4$                                                | $P_0 P_1$                                 | $P_2 P_3$ | $P_4 P_0$ | $P_1 P_2$ | $P_3 P_4$ | $P_0 P_1$ | $P_2 P_3$ | $P_4 P_0$ | $P_1 P_2$ | $P_3 P_4$ |  |  |  |  |  |

| MS: $P_0 P_3 P_1 P_4 P_2$                                                | $P_0 P_3$                                 | $P_1 P_4$ | $P_2 P_0$ | $P_3 P_1$ | $P_4 P_2$ | $P_0 P_3$ | $P_1 P_4$ | $P_2 P_0$ | $P_3 P_1$ | $P_4 P_2$ |  |  |  |  |  |

Fig. 4.  $kr \rightarrow r$  redistribution with normal sequence  $< P_0, P_1, P_2, P_3, P_4>$  and mapping sequence  $< P_0, P_3, P_1, P_4, P_2>$ .

amount of data that is retained on the local array is Mr. In a  $kr \rightarrow r$  redistribution, GCC = Mkr, therefore, the ratio between local data and the number of array elements in a GCC is

$$Mr:GCC=Mr:Mkr=1:k.$$

This is equal to  $\left\lceil \frac{k}{M} \right\rceil : k = 1 : k$ , when k < M.

If  $k \ge M$ , then at most  $\lceil \frac{k}{M} \rceil$  elements are retained on local array in each local complete cycle. Since there are M local complete cycles in a GCC, the total amount of data retained on local array is  $Mr \times \lceil \frac{k}{M} \rceil$ . In a  $kr \to r$  redistribution, GCC = Mkr, therefore, the ratio between local data and the number of array elements in a GCC is  $Mr : GCC = Mr \times \lceil \frac{k}{M} \rceil : Mkr = \lceil \frac{k}{M} \rceil : k$ .

From the above description, the maximum ratio is  $\lceil \frac{k}{M} \rceil : k$ .

2. In a kr → r redistribution, each GCC has the same communication patterns, therefore, we only need to prove that the mapping sequence can achieve the maximum ratio [k/M]: k in the first GCC. In a kr → r redistribution, there are M local complete cycles in each GCC and are denoted as LCC<sub>0</sub>, LCC<sub>1</sub>,..., and LCC<sub>M-1</sub>, respectively.

If k < M, in the source distribution, the source processors of array elements in  $LCC_0$ ,  $LCC_1$ ,..., and  $LCC_{M-1}$  (i.e., A[1:kr], A[kr+1:2kr],..., and  $A[(M-1)\times kr+1:Mkr]$ ) are  $P_0$ ,  $P_1$ ,, and  $P_{M-1}$ , respectively. In the destination distribution, the destination processors of the first r array elements of local complete cycles  $LCC_0$ ,  $LCC_1$ ,..., and  $LCC_{M-1}$  (i.e., A[1:r],

$$A[kr+1:kr+r],\ldots,$$

and

$$A[(M-1) \times kr + 1 : (M-1) \times kr + kr])$$

are  $P_0$ ,  $P_{k \mod M}$ ,  $P_{2k \mod M}$ , ..., and  $P_{(M-1)k \mod M}$ , respectively. According to (1), the new logical

processor ranks for  $P_0$ ,  $P_{k \bmod M}$ ,  $P_{2k \bmod M}$ , ..., and  $P_{(M-1)k \bmod M}$  are equal to  $\alpha(0) = 0$

$$\alpha(k \bmod M) = 1,$$

$$\alpha(2k \bmod M) = 2, \ldots, \text{ and }$$

$$\alpha((M-1) \bmod M) = M-1,$$

respectively. Therefore, there are *Mr* array elements retained on the same logical processor in the source and destination distribution in a *GCC*. The ratio between local data and global array size in a *GCC* is equal to

$$Mr:GCC = Mr:Mkr = 1:k.$$

This is equal to  $\left\lceil \frac{k}{M} \right\rceil$  : k=1: k, when k < M That means the mapping sequence can achieve the ratio 1: k.

For the case of  $k \ge M$ , the proof of this part is similar to above. Therefore, from these two parts, we know that (1) can determine a logical sequence of destination processors to achieve the maximum ratio  $\left\lceil \frac{k}{M} \right\rceil : k$ , between local data and global array size.

**B.**  $P \neq Q$ : Given a  $kr_{(P)} \rightarrow r_{(Q)}$  redistribution on a one-dimensional array A[1:N], we use  $< q_0, q_1, q_2, , q_{Q-1} >$  and  $< q_{\chi(0)}, q_{\chi(1)}, q_{\chi(2)}, \dots, q_{\chi(Q-1)} >$  to represent the normal sequence and the mapping sequence, respectively, where  $\chi(j)$  represents the new logical processor rank of  $q_j$ . For a destination processor  $q_j$ , the new logical processor rank of  $q_j$  can be determined by the following equation:

$$\chi(j) = (j \bmod k) \times \left\lceil \frac{Q}{k} \right\rceil = \left\lfloor \frac{j}{k} \right\rfloor,$$

(2)

where j = 0 to Q - 1.

An example of the generalized processor mapping technique for  $kr_{(P)} \rightarrow r_{(Q)}$  redistribution with different source and destination processor sets is shown in Fig. 5. In Fig. 5, there are four source processors and eight destination processors. According to (2), the mapping sequence of

| Source Distribution: BLOCK-CYCLIC(10)                                                                                       |                                                                          |             |                |                       |             |             |             |                |             |             |                |                |  |

|-----------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------|----------------|-----------------------|-------------|-------------|-------------|----------------|-------------|-------------|----------------|----------------|--|

| Global Array Index $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                    |                                                                          |             |                |                       |             |             |             |                |             |             |                |                |  |

|                                                                                                                             | $P_0$                                                                    | $P_1$       | P <sub>2</sub> | <b>P</b> <sub>3</sub> | $P_0$       | $P_1$       | $P_2$       | P <sub>3</sub> | $P_0$       | $P_1$       | P <sub>2</sub> | P <sub>3</sub> |  |

| <b>\</b>                                                                                                                    |                                                                          |             |                |                       |             |             |             |                |             |             |                |                |  |

| De                                                                                                                          | estinat                                                                  | ion Di      | stribut        | ion: B                | LOCK-       | -CYCI       | JC(5)       | ı              |             |             |                |                |  |

| Global Array Index                                                                                                          | Global Array Index $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |             |                |                       |             |             |             |                |             |             |                | 111 ~<br>120   |  |

| NS: q <sub>0</sub> q <sub>1</sub> q <sub>2</sub> q <sub>3</sub> q <sub>4</sub> q <sub>5</sub> q <sub>6</sub> q <sub>7</sub> | $q_0 q_1$                                                                | $q_2$ $q_3$ | $q_4 \ q_5$    | $q_6 q_7$             | $q_0 q_1$   | $q_2$ $q_3$ | $q_4 \ q_5$ | $q_6 q_7$      | $q_0 q_1$   | $q_2 q_3$   | q4 q5          | $q_6  q_7$     |  |

| MS: $q_0 \ q_4 \ q_1 \ q_5 \ q_2 \ q_6 \ q_3 \ q_7$                                                                         | $q_0$ $q_4$                                                              | $q_1$ $q_5$ | $q_2$ $q_6$    | $q_3$ $q_7$           | $q_0$ $q_4$ | $q_1$ $q_5$ | $q_2$ $q_6$ | $q_3$ $q_7$    | $q_0$ $q_4$ | $q_1$ $q_5$ | $q_2$ $q_6$    | $q_3$ $q_7$    |  |

Fig. 5.  $kr_{(P)} \rightarrow r_{(Q)}$  redistribution on A[1:N] with different sequence of destination processor ranks, where k=2, r=5, N=120, P=4, Q=8.

destination processors  $q_0, q_1, q_2, q_3, q_4, q_5, q_6$ , and  $q_7$  are equal to 0, 4, 1, 5, 2, 6, 3, and 7, respectively. In the mapping sequence scheme, there are 20 array elements retained locally in a global complete cycle. Since GCC=40, the ratio between local data and global array size is equal to 20:40=1:2. According to Lemma 3, the mapping sequence of  $< q_0, q_1, q_5, q_2, q_6, q_3, q_7>$  achieves the maximum ratio  $\left\lceil \frac{k}{Q} \right\rceil:k$  for the redistribution shown in Fig. 5. The following Lemma shows that the generalized processor mapping technique can achieve the maximum amount of data retained locally for  $kr_{(P)} \rightarrow r_{(Q)}$  redistribution, if  $LCC_s$  is equal to kr.

**Lemma 4.** Given a  $kr_{(P)} \rightarrow r_{(Q)}$  redistribution on a one-dimensional array A[1:N]: If  $LCC_s = kr$ , (2) determines a mapping sequence of destination processors to achieve the maximum ratio  $\left\lceil \frac{k}{Q} \right\rceil$ : k between local data and global array size.

**Proof.** We prove the lemma in two parts: 1) The maximum ratio is  $\left\lceil \frac{k}{Q} \right\rceil$ : k. 2) The mapping sequence generated by (2) can achieve the maximum ratio.

1. Given a  $kr_{(P)} \rightarrow r_{(Q)}$  redistribution, for a source processor  $P_i$ , where  $0 \le i \le P-1$ : If k < Q, then at most r elements are retained on the local array in each local complete cycle. Since there are P local complete cycles in a GCC, the total amount of data retained on the local array is Pr. In a  $kr_{(P)} \rightarrow r_{(Q)}$  redistribution, GCC = Pkr, therefore, the ratio between local data and the number of array elements in a GCC is

$$Pr:GCC = Pr:Pkr = 1:k.$$

This is equal to  $\left\lceil \frac{k}{Q} \right\rceil : k = 1 : k$ , when k < Q.

If  $k \ge Q$ , then at most  $\left\lceil \frac{k}{Q} \right\rceil$  elements are retained on local array in each local complete cycle. Since there are P local complete cycles in a GCC, the total amount of data that is retained

on the local array is  $Pr \times \left\lceil \frac{k}{Q} \right\rceil$ . In a  $kr_{(P)} \to r_{(Q)}$  redistribution, GCC = Pkr, therefore, the ratio between the local data and the number of array elements in a GCC is

$$Pr \times \left\lceil \frac{k}{Q} \right\rceil : GCC = Pr \times \left\lceil \frac{k}{Q} \right\rceil : Pkr = \left\lceil \frac{k}{Q} \right\rceil : k.$$

From the above description, the maximum ratio between local data and global array size is  $\left\lceil \frac{k}{Q} \right\rceil : k$ .

2. In a  $kr_{(P)} \rightarrow r_{(Q)}$  redistribution, each *GCC* has the same communication patterns, therefore, we only need to prove that the generalized processor mapping technique can achieve the maximum ratio  $\left\lceil \frac{k}{Q} \right\rceil : k$  in the first *GCC*. In a  $kr_{(P)} \rightarrow r_{(Q)}$  redistribution, there are P local complete cycles in each *GCC* and are denoted as  $LCC_0$ ,  $LCC_1$ ,..., and  $LCC_{P-1}$ , respectively.

If k < Q, in the source distribution, the source processors of array elements in  $LCC_0$ ,  $LCC_1$ ,..., and  $LCC_{P-1}$  (i.e., A[1:kr], A[kr+1:2kr],..., and  $A[(M-1) \times kr+1:Mkr]$ ) are  $p_0$ ,  $p_1$ ,..., and  $p_{(P-1)}$ , respectively. In the destination distribution, the destination processors of the first r array elements of local complete cycles  $LCC_0$ ,  $LCC_1$ ,  $LCC_2$ ,..., and  $LCC_{P-1}$  (i.e.,

$$A[kr+1:kr+r],\ldots,$$

and

$$A[(M-1) \times kr + 1 : (M-1) \times kr + kr])$$

are  $q_0$ ,  $q_{k \bmod Q}$ ,  $q_{2k \bmod Q}$ , ..., and  $q_{(Q-1)k \bmod Q}$ , respectively. According to (2), the new logical processor ranks for  $q_0$ ,  $q_{k \bmod Q}$ ,  $q_{2k \bmod Q}$ , ..., and  $q_{(Q-1)k \bmod Q}$  are equal to  $\chi(0) = 0$ ,  $\chi(k \bmod Q) = 1$ ,  $\chi(2k \bmod Q) = 2$ , ..., and

$$\chi((Q-1)k \bmod Q) = Q-1,$$

| Source Distribution: BLOCK-CYCLIC(5)                                                                                                                                                                                                                                                                                                                      |  |  |  |          |  |  |  |  |  |  |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|----------|--|--|--|--|--|--|

| Global Array Index $\begin{bmatrix} 1 \\ 0 \end{bmatrix} = \begin{bmatrix} 11 \\ 20 \end{bmatrix} = \begin{bmatrix} 21 \\ 30 \end{bmatrix} = \begin{bmatrix} 31 \\ 41 \end{bmatrix} = \begin{bmatrix} 51 \\ 60 \end{bmatrix} = \begin{bmatrix} 61 \\ 70 \end{bmatrix} = \begin{bmatrix} 81 \\ 90 \end{bmatrix} = \begin{bmatrix} 91 \\ 100 \end{bmatrix}$ |  |  |  |          |  |  |  |  |  |  |

| $P_0 P_1 P_2 P_3 P_4 P_0 P_1 P_2 P_3 P_4$                                                                                                                                                                                                                                                     |  |  |  |          |  |  |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                           |  |  |  | <b>\</b> |  |  |  |  |  |  |

| Destination Distribution: BLOCK-CYCLIC(10)                                            |       |       |                |                       |       |       |       |                |                       |       |

|---------------------------------------------------------------------------------------|-------|-------|----------------|-----------------------|-------|-------|-------|----------------|-----------------------|-------|

| Global Array Index $\begin{array}{c ccccccccccccccccccccccccccccccccccc$              |       |       |                |                       |       |       |       |                |                       |       |

| NS: $P_0 P_1 P_2 P_3 P_4$                                                             | $P_0$ | $P_1$ | P <sub>2</sub> | <b>P</b> <sub>3</sub> | $P_4$ | $P_0$ | $P_1$ | P <sub>2</sub> | <b>P</b> <sub>3</sub> | $P_4$ |

| $MS: P_0 P_2 P_4 P_1 P_3$ $P_0$ $P_2$ $P_4$ $P_1$ $P_3$ $P_0$ $P_2$ $P_4$ $P_1$ $P_3$ |       |       |                |                       |       |       |       |                |                       |       |

Fig. 6.  $r \rightarrow kr$  redistribution with normal sequence  $< P_0, P_1, P_2, P_3, P_4>$  and mapping sequence  $< P_0, P_{2,P}, P_4, P_1, P_3>$ .

respectively. Therefore, there are *Pr* array elements retained on the same logical processor in the source and destination distribution in a *GCC*. The ratio between local data and global array size in a *GCC* is equal to

$$Pr:GCC = Pr:Pkr = 1:k.$$

Since k < Q, we have  $\left\lceil \frac{k}{Q} \right\rceil : k = 1 : k$ . That means the mapping sequence can achieve the ratio  $\left\lceil \frac{k}{Q} \right\rceil : k = 1 : k$ .

For the case of  $k \geq Q$ , the proof of this part is similar to above. Therefore, we know that (2) can determine a logical sequence of destination processors to achieve the maximum ratio  $\left\lceil \frac{k}{Q} \right\rceil : k$ , between local data and global array size.

#### 4.1.2 $r_{(P)} \rightarrow kr_{(Q)}$ Array Redistribution

**A.**  $\mathbf{P}=\mathbf{Q}$ : In this section, we present the generalized processor mapping technique for  $r_{(P)} \to k r_{(Q)}$  array redistribution with same source and destination processor sets. Given an  $r \to kr$  redistribution on a one-dimensional array A[1:N] over M processors, we use  $< P_0, P_1, P_2, \ldots, P_{M-1} >$  and

$$< P_{\beta(0)}, P_{\beta(1)}, P_{\beta(2)}, \dots, P_{\beta(M-1)} >$$

to represent the normal sequence and the mapping sequence, respectively, where  $\beta(j)$  represents the new logical processor rank of  $P_j$ . For a destination processor  $P_j$ , the new logical processor rank of  $P_j$  can be determined by the following equation:

$$\beta(j) = (j \mod k) \times \left\lceil \frac{M}{k} \right\rceil + \left\lceil \frac{j \times k}{M} \right\rceil,$$

(3)

where j = 0 to M - 1.

Fig. 6 shows a BLOCK-CYCLIC(5) to BLOCK-CYCLIC(10) redistribution on a one-dimensional array A[1:100] over five processors. In Fig. 6, two kinds of logical processor

sequences are illustrated. The normal sequence of the destination processor ranks is  $P_0$ ,  $P_1$ ,  $P_2$ ,  $P_3$ , and  $P_4$ . According to (3), the new ranks of destination processors  $P_0$ ,  $P_1$ ,  $P_2$ ,  $P_3$ , and  $P_4$  are equal to 0, 2, 4, 1, and 3, respectively. Therefore, the mapping sequence of destination processors is  $P_0$ ,  $P_2$ ,  $P_4$ ,  $P_1$ , and  $P_3$ . From Fig. 6, we can see that there are 20 array elements retained locally in the normal sequence scheme while there are 50 array elements retained locally in a mapping sequence scheme. The generalized processor mapping technique provides a larger amount of local data. The following lemma states that the mapping sequence generated by (3) can achieve the maximum amount of data that is retained on the same logical processor through an  $r \to kr$  redistribution.

**Lemma 5.** Given an  $r \to kr$  redistribution on a one-dimensional array A[1:N] over M processors, (3) determines a mapping sequence of destination processors to achieve the maximum ratio  $\left\lceil \frac{k}{M} \right\rceil$ : k between local data and the global array size.

**Proof.** The proof of this lemma can be easily established according to Lemma 3.

**B.**  $P \neq Q$ : Given an  $r_{(P)} \rightarrow kr_{(Q)}$  redistribution on a one-dimensional array A[1:N], we use  $< q_0, q_1, q_2, \ldots, q_{Q-1} >$  and  $< q_{\delta(0)}, q_{\delta(1)}, q_{\delta(2)}, \ldots, q_{\delta(Q-1)} >$  to represent the normal sequence and the mapping sequence, respectively, where  $\delta(j)$  represents the new logical processor rank of  $q_j$ . For a destination processor  $q_j$ , the new logical processor rank of  $q_j$  can be determined by the following equation:

$$\delta(j) = (j \bmod k) \times \left\lceil \frac{Q}{k} \right\rceil + \left| \frac{j \times k}{Q} \right|, \tag{4}$$

where j = 0 to Q - 1.

**Lemma 6.** Given an  $r_{(P)} \to kr_{(Q)}$  redistribution on a one-dimensional array A[1:N], if  $LCC_d = kr$ , (4) determines a logical sequence of destination processors to achieve the maximum ratio  $\left\lceil \frac{k}{Q} \right\rceil$ , between local data and global array size.

| Source Distribution: BLOCK-CYCLIC(10) |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |             |                       |             |             |             |             |             |             |              |              |

|---------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|-----------------------|-------------|-------------|-------------|-------------|-------------|-------------|--------------|--------------|

| Global Array Index                    | 1 ~<br>10                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 11 ~<br>20  | 21 ~<br>30  | 31 ~<br>40            | 41 ~<br>50  | 51 ~<br>60  | 61 ~<br>70  | 71 ~<br>80  | 81 ~<br>90  | 91 ~<br>100 | 101 ~<br>110 | 111 ~<br>120 |

|                                       | $P_0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | $P_1$       | $P_2$       | <b>P</b> <sub>3</sub> | $P_0$       | $P_1$       | $P_2$       | $P_3$       | $P_0$       | $P_1$       | $P_2$        | $P_3$        |

| <b>+</b>                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |             |             |                       |             |             |             |             |             |             |              |              |

| Do                                    | estinat                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ion Di      | stribut     | ion: B                | LOCK-       | -CYCI       | JC(5)       | (           |             |             |              |              |

| Global Array Index                    | Global Array Index $\begin{vmatrix} 1 \\ 10 \end{vmatrix} = \begin{vmatrix} 11 \\ 20 \end{vmatrix} = \begin{vmatrix} 21 \\ 30 \end{vmatrix} = \begin{vmatrix} 31 \\ 40 \end{vmatrix} = \begin{vmatrix} 41 \\ 50 \end{vmatrix} = \begin{vmatrix} 51 \\ 60 \end{vmatrix} = \begin{vmatrix} 61 \\ 70 \end{vmatrix} = \begin{vmatrix} 71 \\ 80 \end{vmatrix} = \begin{vmatrix} 91 \\ 90 \end{vmatrix} = \begin{vmatrix} 101 \\ 110 \end{vmatrix} = \begin{vmatrix} 111 \\ 120 \end{vmatrix}$ |             |             |                       |             |             |             |             |             |             |              |              |

| $NS: P_0 P_1 P_2 P_3 P_4 P_5$         | $P_0$ $P_1$                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $P_2$ $P_3$ | $P_4$ $P_5$ | $P_0$ $P_1$           | $P_2$ $P_3$ | $P_4$ $P_5$ | $P_0$ $P_1$ | $P_2$ $P_3$ | $P_4$ $P_5$ | $P_0$ $P_1$ | $P_2$ $P_3$  | $P_4$ $P_5$  |

| $MS: P_0 P_3 P_1 P_4 P_2 P_5$         | $P_0$ $P_3$                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | $P_1$ $P_4$ | $P_2$ $P_5$ | $P_0$ $P_3$           | $P_1$ $P_4$ | $P_2$ $P_5$ | $P_0$ $P_3$ | $P_1$ $P_4$ | $P_2$ $P_5$ | $P_0$ $P_3$ | $P_1$ $P_4$  | $P_2$ $P_5$  |

Fig. 7.  $kr_{(P)} \rightarrow r_{(Q)}$  redistribution on A[1:N] with different sequence of destination processor ranks, where k=2, r=5, N=120, P=4, Q=6.

**Proof.** The proof of this lemma can be easily established according to Lemma 4.

#### 4.2 General Type

According to Table 1, there are two types of redistribution in the general type:  $kr_{(P)} \rightarrow r_{(Q)}$  redistribution with  $LCC_s \neq kr$  and  $r_{(P)} \rightarrow kr_{(Q)}$  redistribution with  $LCC_d \neq kr$ . For  $kr_{(P)} \rightarrow r_{(Q)}$  redistribution, the mapping function is the same as (2). For  $r_{(P)} \rightarrow kr_{(Q)}$  redistribution, the mapping function is the same as (4). Fig. 7 shows an example of  $kr_{(P)} \rightarrow r_{(Q)}$  redistribution with  $LCC_s = 3kr$ . According to (2), the mapping sequence is  $P_0, P_3, P_1, P_4, P_2, P_5$ . In Fig. 7, both the normal sequence scheme and the mapping sequence scheme provide the same amount of local data. The generalized processor mapping technique does not provide a larger amount of local data than that of the normal method in this case. Fig. 8 shows another example of  $kr_{(P)} \rightarrow r_{(Q)}$  redistribution with  $LCC_s = 2kr$ . According to (2), the mapping sequence is

$$P_0, P_6, P_1, P_7, P_2, P_8, P_3, P_9, P_4, P_{10}, P_5, P_{11}.$$

In Fig. 8, the mapping sequence scheme provides a larger amount of local data than that of the normal sequence scheme. From the above two examples, we know that the processor mapping technique provides a different improvement for different  $kr_{(P)} \rightarrow r_{(Q)}$  redistribution. In Section 6, we will present a theoretical model to analyze the amount of local data in the generalized processor mapping technique. The mathematical model can also calculate the improvement of the generalized processor mapping technique for  $kr_{(P)} \rightarrow r_{(Q)}$  redistribution or vice versa.

#### 5 MULTIDIMENSIONAL ARRAY REDISTRIBUTION

The generalized processor mapping technique can be extended to multidimensional arrays. To simplify the presentation, we use

$$BC(k_0r_0, k_1r_1, \dots, k_{n-1}r_{n-1}) \to BC(r_0, r_1, \dots, r_{n-1})$$

to represent an n-dimensional (BLOCK-CYCLIC( $k_0r_0$ ), BLOCK-CYCLIC( $k_1r_1$ ),..., BLOCK-CYCLIC( $k_{n-1}r_{n-1}$ )) to (BLOCK-CYCLIC( $r_0$ ), BLOCK-CYCLIC( $r_1$ ),..., BLOCK-CYCLIC( $r_{n-1}$ )) redistribution and

| Source Distribution: BLOCK-CYCLIC(10)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                               |                               |                       |                               |                              |                       |                               |             |                |                                   |              |                |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------|-------------------------------|-----------------------|-------------------------------|------------------------------|-----------------------|-------------------------------|-------------|----------------|-----------------------------------|--------------|----------------|

| Global Array Index                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 1 ~<br>10                     | 11 ~<br>20                    | 21 ~<br>30            | 31 ~<br>40                    | 41 ~<br>50                   | 51 ~<br>60            | 61 ~<br>70                    | 71 ~<br>80  | 81 ~<br>90     | 91 ~<br>100                       | 101 ~<br>110 | 111 ~<br>120   |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | $P_0$                         | $P_1$                         | <b>P</b> <sub>2</sub> | $P_0$                         | $P_1$                        | P <sub>2</sub>        | $P_0$                         | $P_1$       | P <sub>2</sub> | $P_0$                             | $P_1$        | P <sub>2</sub> |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                               |                               |                       |                               |                              |                       |                               |             |                |                                   |              |                |

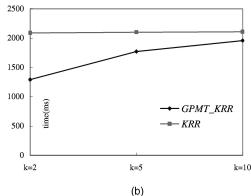

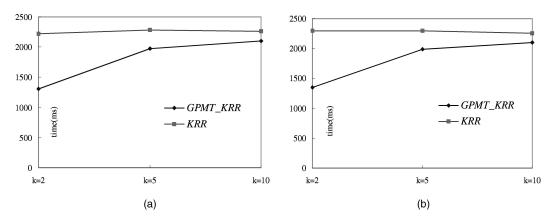

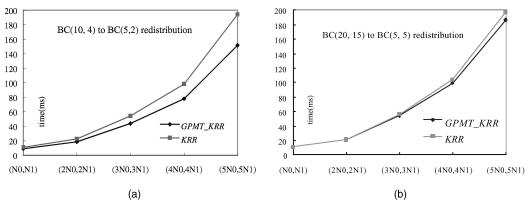

| Destination Distribution: BLOCK-CYCLIC(5)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                               |                               |                       |                               |                              |                       |                               |             |                |                                   |              |                |