CS4100: 計算機結構

### Designing a Multicycle Processor

國立清華大學資訊工程學系 九十三學年度第一學期

Adapted from class notes of D. Patterson Copyright 1998, 2000 UCB

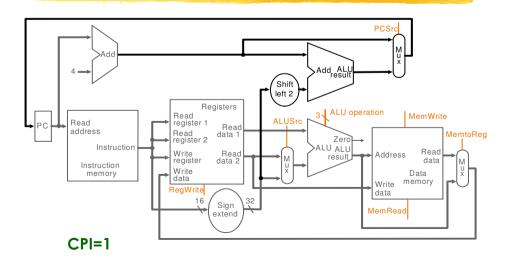

#### Recap: A Single-Cycle Processor

| 図 三清 辛 大 学 Multicycle Design-2 | National Tsing Hua University Computer Architecture CTKing/TTHwang

#### Outline

- Designing a processor

- Building the datapath

- ♦ A single-cycle implementation

- ♦ A multicycle implementation

- Microprogramming: simplifying control (Appendix C.4)

- **♦** Exceptions

Multicycle Design-1

Computer Architecture CTKing/TTHwang

### What's Wrong with Single-cycle?

|            |             |              | A CONTRACTOR OF THE PROPERTY OF THE PARTY OF |           |           |

|------------|-------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------|-----------|

| Arithmetic | & Logical   |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |           |

| PC         | Inst Memory | Reg File     | mux ALU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | mux setup |           |

|            |             | -            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |           |

| Load       |             |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |           |

| PC         | Inst Memory | Reg File     | mux ALU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Data Mem  | mux setup |

| *          |             | — Critical I | Path ———                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |           |           |

| Store      |             | C            | a                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |           |           |

| PC         | Inst Memory | Reg File     | mux ALU                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Data Mem  |           |

|            |             |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |           |

| Branch     |             |              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |           |           |

| PC         | Inst Memory | Reg File     | cmp mux                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |           |           |

- Long cycle time

- All instructions take same time as the slowest

- Real memory is not so ideal

- cannot always get job done in one (short) cycle

- A FU can only be used once => higher cost

#### Outline

- Designing a processor

- Building the datapath

- ♦ A single-cycle implementation

- ♦ A multicycle implementation

- Multicycle datapath

- Multicycle execution steps

- Multicycle control (Appendix C.3)

- Microprogramming: simplifying control (Appendix C.4)

- Exceptions

Multicycle Design-4

Computer Architecture CTKing/TTHwang

#### Multicycle Implementation

Reduce cycle time

National Tsing Hua University

National Tsing Hua University

- Diff. Inst. take diff. cycles

- Share functional units

Multicycle Design-5

Computer Architecture CTKing/TTHwang

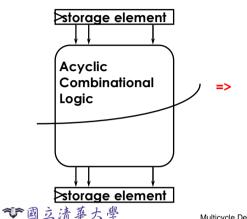

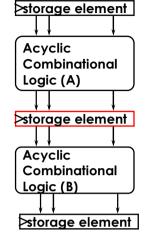

### Multicycle Approach

- Break up the instructions into steps, each step takes a cycle

- balance the amount of work to be done

- restrict each cycle to use only one major functional unit

- At the end of a cycle

- store values for use in later cycles (easiest thing to do)

- introduce additional internal registers

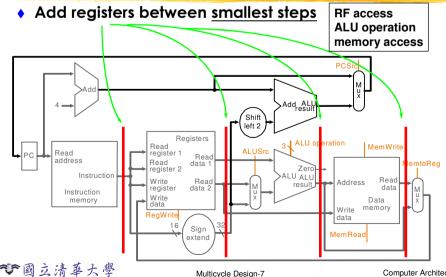

### Partition Single-Cycle Datapath

Computer Architecture CTKing/TTHwang

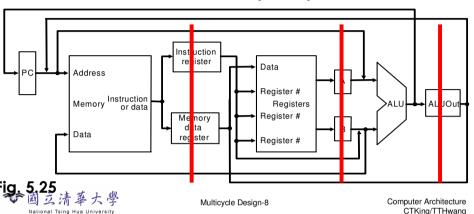

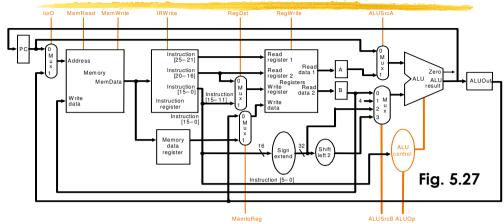

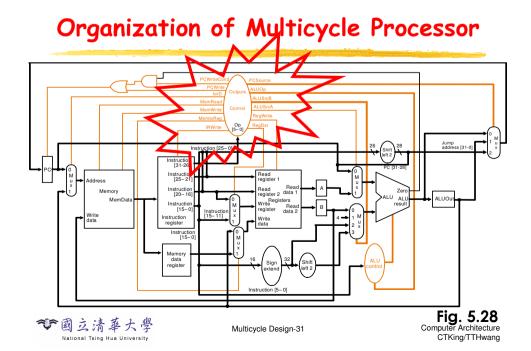

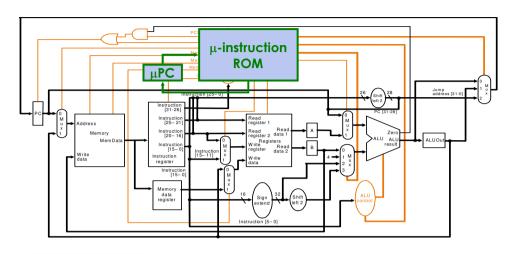

#### Multicycle Datapath

- 1 memory (instr. & data), 1 ALU (addr, PC+4, add,...), registers (IR, MDR, A, B, ALUOut)

- Storage for subsequent inst. (arch.-visible) vs. storage for same inst. but in a subsequent cycle

#### Multicycle Datapath for Basic Instr.

- ◆ IR needs write control, but others don't

- MUX to select 2 sources to memory; memory needs read signal

- PC and A to one ALU input; four sources to another input

Multicycle Design-9

Computer Architecture CTKing/TTHwang

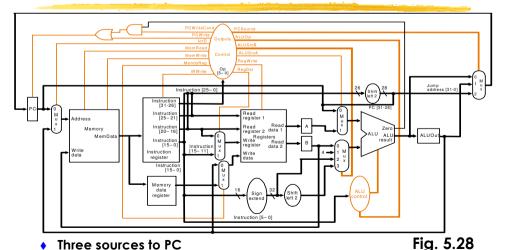

## Adding Branch/Jump

#### Outline

- Designing a processor

- Building the datapath

- ◆ A single-cycle implementation

- A multicycle implementation

- Multicycle datapath

- Multicycle execution steps

- Multicycle control (Appendix C.3)

- Microprogramming: simplifying control (Appendix C.4)

- Exceptions

Two PC write signals

National Tsing Hua University

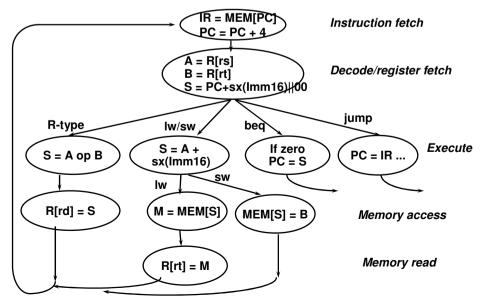

#### Five Execution Steps

- Instruction Fetch

- Instruction Decode and Register Fetch

- Execution, Memory Address Computation, or Branch Completion

- Memory Access or R-type Instruction Completion

- Memory Read Completion (Write-back)

**INSTRUCTIONS TAKE FROM 3 - 5 CYCLES!**

Multicycle Design-12

Computer Architecture . CTKing/TTHwang

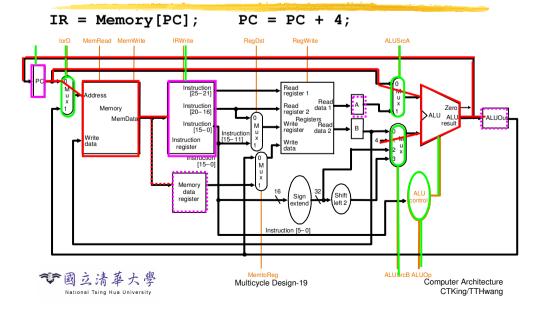

#### Step 1: Instruction Fetch

- Use PC to get instruction and put it in the Instruction Register (IR)

- Increment the PC by 4 and put the result back in the

- Can be described succinctly using RTL (Register-Transfer Lanauage)

```

IR = Memory[PC];

PC = PC + 4:

```

Can we figure out the values of the control signals?

What is the advantage of updating the PC now?

Multicycle Design-13

Computer Architecture CTKing/TTHwang

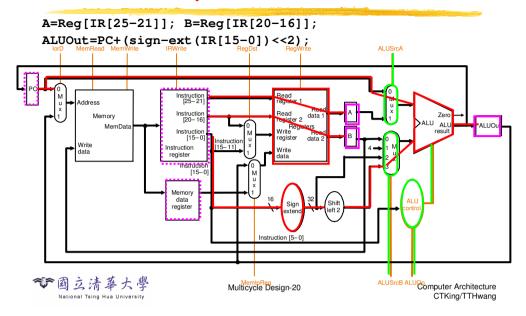

#### Step 2: Instruction Decode and Register Fetch

- Read registers rs and rt in case needed

- Compute the branch address in case the instruction is a branch

- RTL:

```

A = Reg[IR[25-21]];

B = Reg[IR[20-16]];

ALUOut=PC+(sign-ext(IR[15-0]) << 2);

```

We aren't setting any control lines based on the instruction type vet (we are busy "decoding" it in control logic)

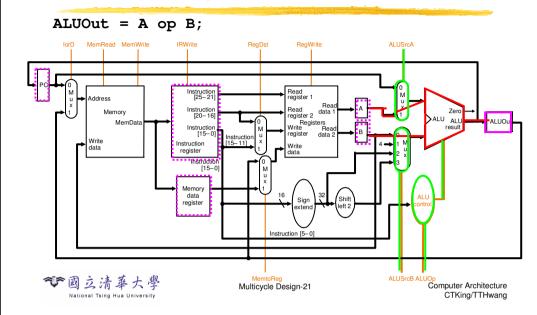

Step 3: Execution

ALU is performing one of three functions, based on instruction type:

```

Memory Reference:

ALUOut = A + sign-extend(IR[15-0]);

```

```

• R-type:

ALUOut = A op B;

```

if (A==B) PC = ALUOut;

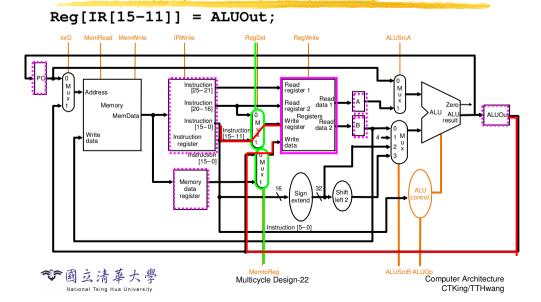

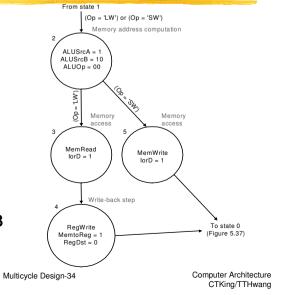

#### Step 4: R-type or Memory-access

Loads and stores access memory

```

MDR = Memory[ALUOut];

Memory[ALUOut] = B;

```

• R-type instructions finish

```

Reg[IR[15-11]] = ALUOut;

```

The write actually takes place at the end of the cycle on the edge

Multicycle Design-16

Computer Architecture CTKing/TTHwang

#### Step 5: Write-back

Loads write to register

$$Reg[IR[20-16]] = MDR;$$

What about all the other instructions?

Multicycle Design-17

Computer Architecture CTKing/TTHwang

### Summary of the Steps

| Step name                                                                                                             | Action for R-type instructions | Action for memory-reference instructions                       | Action for branches            | Action for jumps                    |  |  |

|-----------------------------------------------------------------------------------------------------------------------|--------------------------------|----------------------------------------------------------------|--------------------------------|-------------------------------------|--|--|

| Instruction fetch                                                                                                     | IR = Memory[PC]<br>PC = PC + 4 |                                                                |                                |                                     |  |  |

| Instruction A = Reg [IR[25-21]] decode/register fetch B = Reg [IR[20-16]] ALUOut = PC + (sign-extend (IR[15-0]) << 2) |                                |                                                                |                                |                                     |  |  |

| Execution, address computation, branch/ iump completion                                                               | ALUOut = A op B                | ALUOut = A + sign-extend<br>(IR[15-0])                         | if (A ==B) then<br>PC = ALUOut | PC = PC [31-28] II<br>(IR[25-0]<<2) |  |  |

| Memory access or R-type completion                                                                                    | Reg [IR[15-11]] =<br>ALUOut    | Load: MDR = Memory[ALUOut]<br>or<br>Store: Memory [ALUOut] = B |                                |                                     |  |  |

| Memory read completion                                                                                                |                                | Load: Reg[IR[20-16]] = MDR                                     |                                |                                     |  |  |

Fig. 5.30

Computer Architecture

### Cycle 1 of add

#### Cycle 2 of add

#### Cycle 3 of add

### Cycle 4 of add

#### Simple Question

How many cycles will it take to execute this code?

lw \$t2, 0(\$t3)

lw \$t3, 4(\$t3)

beq \$t2, \$t3, Label

add \$t5, \$t2, \$t3

sw \$t5, 8(\$t3)

Label: ..

- What is going on during the 8th cycle of execution?

- In what cycle does the actual addition of \$t2 and \$t3 takes place?

#### Outline

- Designing a processor

- Building the datapath

- ♦ A single-cycle implementation

- ♦ A multicycle implementation

- Multicycle datapath

- Multicycle execution steps

- Multicycle control (Appendix C.3)

- Microprogramming: simplifying control (Appendix C.4)

- Exceptions

Multicycle Design-24

Computer Architecture CTKing/TTHwang

> . CTKing/TTHwang

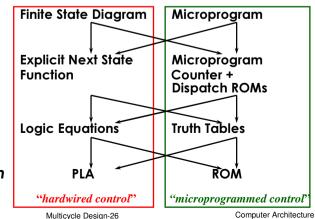

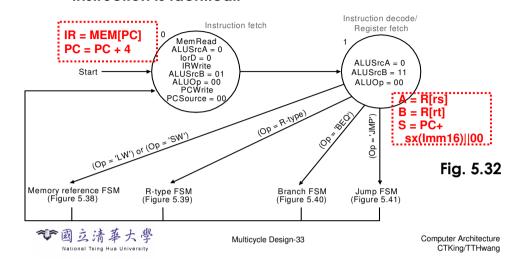

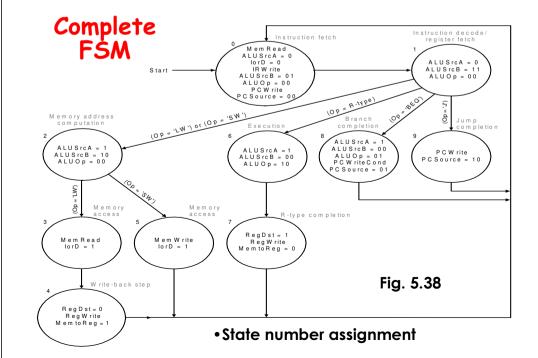

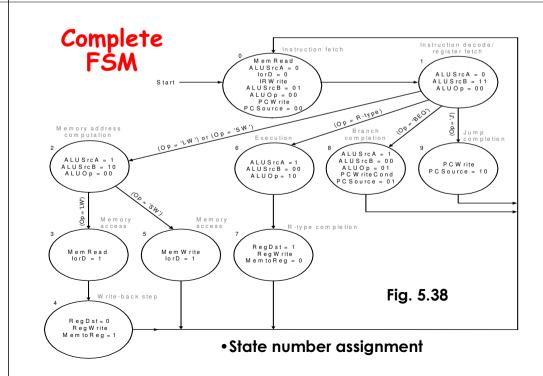

#### Implementing the Control

- Value of control signals is dependent upon:

- what instruction is being executed

- which step is being performed

- Control must specify both the signals to be set in any step and the next step in the sequence

- Control specification

- Use a finite state machine (graphically)

- Use microprogramming

- Implementation can be derived from the specification and use gates, ROM, or PLA

Multicycle Design-25

Computer Architecture CTKing/TTHwang

#### Controller Design: An Overview

Several possible initial representations, sequence control and logic representation, and control implementation => all may be determined indep.

Initial Rep.

Sequencing Control

Logic Rep.

National Tsing Hua University

*Implementation*

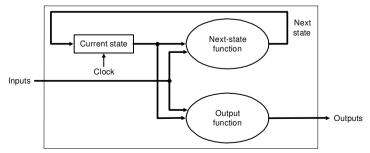

#### Review: Finite State Machines

- Finite state machines:

- a set of states and

- next state (set by current state and input)

- output (set by current state and possibly input)

We will use a Moore Machine (output based only on the current state)

Multicycle Design-27

Computer Architecture CTKing/TTHwang

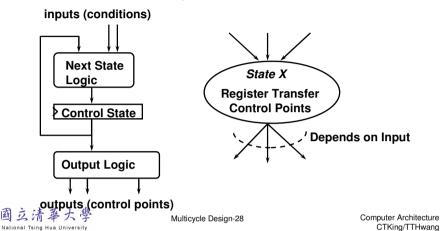

#### Our Control Model

- State specifies control points for RT

- Transfer at exiting state (same falling edge)

- One state takes one cycle

#### Summary of the Steps

| Step name                                               | Action for R-type instructions                                                            | Action for memory-reference instructions                       | Action for branches            | Action for jumps                    |  |  |

|---------------------------------------------------------|-------------------------------------------------------------------------------------------|----------------------------------------------------------------|--------------------------------|-------------------------------------|--|--|

| Instruction fetch                                       | IR = Memory[PC]<br>PC = PC + 4                                                            |                                                                |                                |                                     |  |  |

| Instruction decode/register fetch                       | A = Reg [IR[25-21]]<br>B = Reg [IR[20-16]]<br>ALUOut = PC + (sign-extend (IR[15-0]) << 2) |                                                                |                                |                                     |  |  |

| Execution, address computation, branch/ jump completion | ALUOut = A op B                                                                           | ALUOut = A + sign-extend<br>(IR[15-0])                         | if (A ==B) then<br>PC = ALUOut | PC = PC [31-28] II<br>(IR[25-0]<<2) |  |  |

| Memory access or R-type completion                      | Reg [IR[15-11]] =<br>ALUOut                                                               | Load: MDR = Memory[ALUOut]<br>or<br>Store: Memory [ALUOut] = B |                                |                                     |  |  |

| Memory read completion                                  |                                                                                           | Load: Reg[IR[20-16]] = MDR                                     |                                |                                     |  |  |

Fig. 5.30

Multicycle Design-29

Computer Architecture CTKing/TTHwang

### Control Specification for Multicycle

#### Control Signals

| 10                 | Signal name        |       |                    | Effect when asserted       |                       |

|--------------------|--------------------|-------|--------------------|----------------------------|-----------------------|

| #                  | ALUSrcA            |       | operand = PC       | 1st ALU operand = Re       | g[rs]                 |

| 2                  | RegWrite           | None  |                    | Reg file is written        |                       |

| 2                  | MemtoReg           |       | ta input = ALU     | Reg. write data input      | = MDR                 |

| $\mathcal{L}$      | RegDst             |       | ite dest. no. = rt | Reg. write dest. no. =     |                       |

| 3.                 | MemRead            | None  |                    | Memory at address is       | read                  |

|                    | MemWrite           | None  |                    | Memory at address is       | written               |

| 2                  | lorD               |       | / address = PC     | Memory address = AL        | .Uout                 |

| 20                 | IRWrite            | None  |                    | IR = Memory                |                       |

| Single Bit Control | PCWrite            | None  |                    | PC = PCSource              |                       |

|                    | PCWriteCond        | None  |                    | If zero then PC = PCS      | ource                 |

|                    | Signal name        | Value | Effect             |                            |                       |

| Control            | ALUOp              | 00    | ALU adds           |                            |                       |

| 45                 | •                  | 01    | ALU subtracts      |                            | ig. 5.29              |

| Ĕ                  |                    | 10    | ALU operates ac    | ccording to func code      | . J                   |

| $\mathcal{Z}$      | ALUSrcB            | 00    | 2nd ALU input =    | : B                        |                       |

| _                  |                    | 01    | 2nd ALU input =    | : 4                        |                       |

| Bit                |                    | 10    | 2nd ALU input =    | sign extended IR[15-0      | 1                     |

| ~                  |                    | 11    | 2nd ALU input =    | siğn ext., shift left 2 IF | <b>{</b> [15-0]       |

| 2                  | PCSource           | 00    | PC = ALU (PC +     | 4)                         |                       |

| · <b>‡</b>         |                    | 01    | PC = ALUout (br    | anch target address)       |                       |

| 73                 | PCSource<br>₹國立清華大 | 10    | PC = PC + 4[31-28] | 3] : IR[25-0] << 2         |                       |

| <b>Z</b> ~         | ヘヨニオオコ             | หรัก  | •                  |                            |                       |

| <                  | 广幽豆清平大             | 学     | Multicycle Desig   | jn-32                      | Computer Architecture |

#### Mapping RT to Control Signals

Instruction fetch and decode portion of every instruction is identical:

### Mapping RT to Control Signals

• FSM for controlling memory reference instructions:

Fig. 5.33

National Tsing Hua University

. CTKing/TTHwang

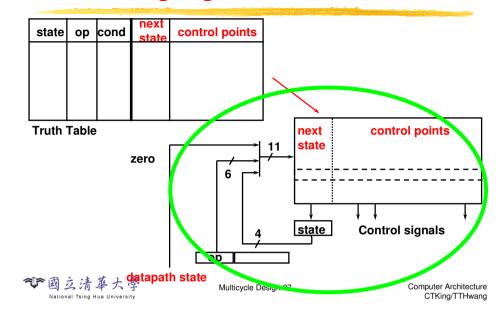

#### From FSM to Truth Table

Please reference the logic equations in Fig. C.3.3 and the truth table in Fig. C.3.6

| Output<br>PCWrite<br>PCWriteCond<br>IorD | Equation<br>state0 + state9<br>state8<br>state3 + state5 | ,     |   |   |    |      |     |    |    |    |   |

|------------------------------------------|----------------------------------------------------------|-------|---|---|----|------|-----|----|----|----|---|

| NextState0                               | Output                                                   |       |   |   | Cı | ırre | ent | st | at | es |   |

|                                          |                                                          | 0     | 1 | 2 | 3  | 4    | 5   | 6  | 7  | 8  | 9 |

| NextState1                               | PCWrite PCWrite                                          | 1     | 0 | 0 | 0  | 0    | 0   | 0  | 0  | 0  | 1 |

| NextState2                               | PCWriteCond                                              | 0     | 0 | 0 | 0  | 0    | 0   | 0  | 0  | 1  | 0 |

| NextState3                               | IorD                                                     | 0     | 0 | 0 | 1  | 0    | 1   | 0  | 0  | 0  | 0 |

| •••                                      |                                                          | • • • | , |   |    |      |     |    |    |    |   |

Multicycle Design-36

Computer Architecture CTKing/TTHwang

#### Designing FSM Controller

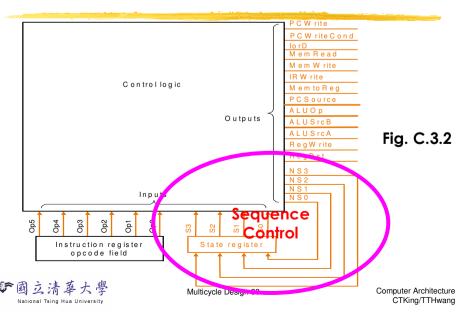

#### The Control Unit

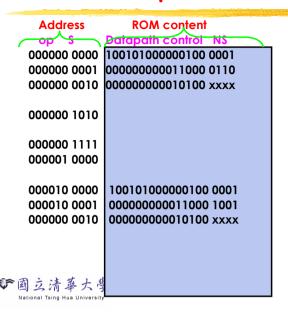

#### ROM Implementation

Need a ROM of 10-bit address, 20-bit word (16-bit datapath control, 4-bit next state)

#### **ROM Implementation (cont.)**

- Rather wasteful, since for lots of entries, outputs are same or are don'tcare

- Could break up into two smaller ROMs (Fig. C.3.7, C.3.8)

Computer Architecture CTKing/TTHwang

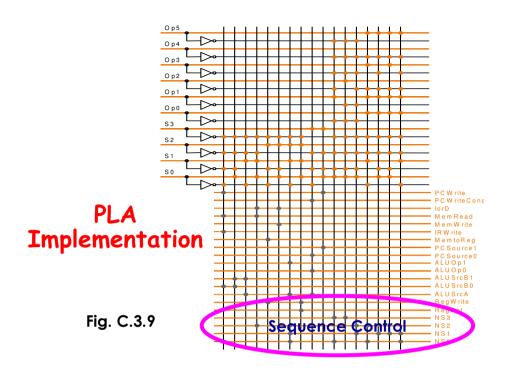

#### ROM vs PLA

- ROM: use two smaller ROMs (Fig. C.3.7, C.3.8)

- 4 state bits give the 16 outputs, 24x16 bits of ROM

- 10 bits give 4 next state bits, 210x 4 bits of ROM

- Total = 4.3K bits of ROM (compared to 2<sup>10</sup>x 20 bits of single ROM implementation)

- PLA is much smaller

- can share product terms

- only need entries that produce an active output

- can take into account don't-cares

- Size is (#inputs × #product-terms) + (#outputs × #product-terms)

For this example = (10x17)+(20x17) = 460 PLA cells

- PLA cells usually about the size of a ROM cell (slightly bigger)

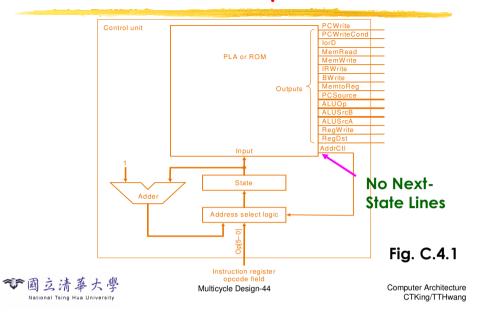

#### Use Counter for Sequence Control

#### **Control Contents**

| Dispatch ROM 1 |             |       |  |  |  |  |  |

|----------------|-------------|-------|--|--|--|--|--|

| Op             | Opcode name | Value |  |  |  |  |  |

| 000000         | R-format    | 0110  |  |  |  |  |  |

| 000010         | jmp         | 1001  |  |  |  |  |  |

| 000100         | beq         | 1000  |  |  |  |  |  |

| 100011         | lw          | 0010  |  |  |  |  |  |

| 101011         | SW          | 0010  |  |  |  |  |  |

| Dispatch ROM 2 |             |  |  |  |  |  |

|----------------|-------------|--|--|--|--|--|

| Opcode name    | Value       |  |  |  |  |  |

| lw             | 0011        |  |  |  |  |  |

| SW             | 0101        |  |  |  |  |  |

|                | Opcode name |  |  |  |  |  |

Fig. C.4.3, C.4.4

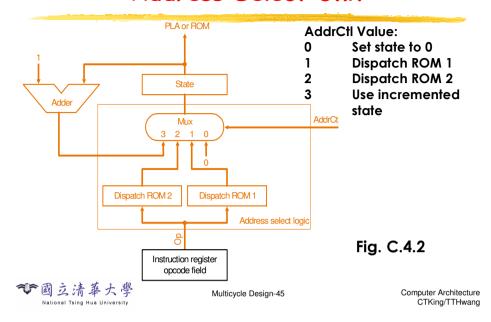

| State number | Address-control action    | Value of AddrCtl |

|--------------|---------------------------|------------------|

| 0            | Use incremented state     | 3                |

| 1            | Use dispatch ROM 1        | 1                |

| 2            | Use dispatch ROM 2        | 2                |

| 3            | Use incremented state     | 3                |

| 4            | Replace state number by 0 | 0                |

| 5            | Replace state number by 0 | 0                |

| 6            | Use incremented state     | 3                |

| 7            | Replace state number by 0 | 0                |

| 8            | Replace state number by 0 | 0                |

| 9            | Replace state number by 0 | 0                |

#### Address Select Unit

#### Outline

- Designing a processor

- Building the datapath

- ♦ A single-cycle implementation

- A multicycle implementation

- Multicycle datapath

- Multicycle execution steps

- Multicycle control

- Microprogramming: simplifying control (Appendix C.4)

- Exceptions

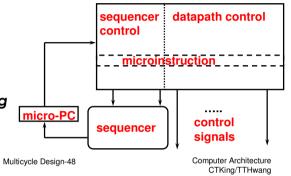

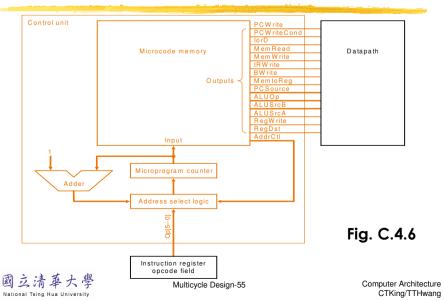

#### Microprogrammed Controller

- Control is the hard part of processor design

- Datapath is fairly regular and well-organized

- Memory is highly regular

- Control is irregular and global

- But, the state diagrams that define the controller for an instruction set processor are highly structured

- Use this structure to construct a simple "microsequencer"

- Control reduces to programming this simple device

- => microprogramming

### Designing a Microinstruction Set

- 1) Start with a list of control signals

- 2) Group signals together that make sense (vs. random): called fields

- 3) Places fields in some logical order (e.g., ALU operation & ALU operands first and microinstruction sequencing last)

- 4) Create a symbolic legend for the microinstruction format, showing name of field values and how they set control signals

- Use computers to design computers

- 5) To minimize the width, encode operations that will never be used at the same time

## Computer Architecture

. CTKing/TTHwang

#### **Microinstruction**

- Control signals:

- Think of the set of control signals that must be asserted in a state as an instruction

- Executing a microinstruction has the effect of asserting the control signal specified by the microinstruction

- Sequencina

- What microinstruction should be executed next?

- Execute sequentially (next state unconditionally)

- Branch (next state also depends on inputs)

- A microprogram is a sequence of microinstructions executing a program flow chart (finite state machine)

Multicycle Design-49

Computer Architecture CTKing/TTHwang

## 1-3) Control Signals and Fields

|              | Signal name                                        | Effect v | vhen deasserted                                      | Effect when asserted               |  |  |  |  |

|--------------|----------------------------------------------------|----------|------------------------------------------------------|------------------------------------|--|--|--|--|

| 10           | ALUSrcA                                            | 1st ALU  | operand = PC                                         | 1st ALU operand = Reg[rs]          |  |  |  |  |

| t            | RegWrite                                           | None     |                                                      | Reg file is written                |  |  |  |  |

| 20           | MemtoReg                                           |          |                                                      | Reg. write data input = MDR RegDst |  |  |  |  |

| Contr        |                                                    | Reg. wr  | ite dest. no. = rt                                   | Reg. write dest. no. = rd          |  |  |  |  |

| it           | MemRead                                            | None     |                                                      | Memory at address is read          |  |  |  |  |

| B            | MemWrite                                           | None     |                                                      | Memory at address is written       |  |  |  |  |

| le           | IorD                                               | Memory   | address = PC                                         | Memory address = ALUout            |  |  |  |  |

| 8            | IRWrite                                            | None     |                                                      | IR = Memory                        |  |  |  |  |

| Single Bit   | <b>PCWrite</b>                                     | None     |                                                      | PC = PCSource                      |  |  |  |  |

| Ţ            | PCWriteCor 4 1 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 2 | nd None  |                                                      | If zero then PC = PCSource         |  |  |  |  |

| 7            | Signal name                                        | Value    | Effect                                               |                                    |  |  |  |  |

| Contro       | ALUOp                                              | 00       | ALU adds                                             |                                    |  |  |  |  |

| 2            | л.=00р                                             | 01       | ALU subtracts                                        |                                    |  |  |  |  |

| $\ddot{c}$   |                                                    | 10       | ALU operates accor                                   | rding to func code                 |  |  |  |  |

| i:           | ALUSrcB                                            | 00       | 2nd ALU input = B                                    | •                                  |  |  |  |  |

| B            |                                                    | 01       | 2nd ALU input = 4                                    |                                    |  |  |  |  |

| e            |                                                    | 10       |                                                      | n extended IR[15-0]                |  |  |  |  |

| <u>a</u>     |                                                    | 11       | 2nd ALU input = sign extended, shift left 2 IR[15-0] |                                    |  |  |  |  |

| Multiple Bit | PCSource                                           | 00       | PC = ALU (PC + 4)                                    |                                    |  |  |  |  |

| Ţ.           |                                                    | 01       | PC = ALUout (brance                                  | ch target address)                 |  |  |  |  |

|              |                                                    | 10       | PC = PC+4[31-28] :                                   | IK[25-0] << 2                      |  |  |  |  |

### 4) Fields and Legend

| Field Name       | Values for Field |                                       |

|------------------|------------------|---------------------------------------|

| ALU control      | Add<br>Subt.     | ALU adds<br>ALU subtracts             |

|                  | Func code        | ALU does function code                |

| SRC1             | PC               | 1st ALU input = PC                    |

|                  | Α                | 1st ALU input = A (Reg[rs])           |

| SRC2             | В                | 2nd ALU input = B`(Reg[rf])           |

|                  | 4                | 2nd ALU input = 4                     |

|                  | Extend           | 2nd ALU input = sign ext. IR[15-0]    |

|                  | Extshft          | 2nd ALU input = sign ex., sl [R[15-0] |

| Register control | Read             | A = Reg[rs]; B = Reg[rt];             |

|                  | Write ALU        | Reg[rd] = ALUout                      |

|                  | Write MDR        | Reg[rt] = MDR                         |

| Memory           | Read PC          | IR (MDR) = mem[PC]                    |

| -                | Read ALU         | MDR = mem[ALƯout]                     |

|                  | Write ALU        | mem[ALUout] = B                       |

| PC write         | ALU              | PC = ALU output                       |

|                  | ALUout-cond.     | IF ALU zero then PC = ALUout          |

|                  | jump addr.       | PC = PCSource                         |

| Sequencing       | Seq              | Go to sequential microinstruction     |

|                  | Fetch            | Go to the first microinstruction      |

|                  | Dispatch 1       | Dispatch using ROM1                   |

|                  | Dispatch 2       | Dispatch using ROM2                   |

### The Microprogram

| Label    | ALU<br>control | SRC1 | SRC2    | Register control | Memory    | PCWrite control | Sequencing |

|----------|----------------|------|---------|------------------|-----------|-----------------|------------|

| Fetch    | Add            | PC   | 4       | 30111101         | Read PC   | ALU             | Seq        |

|          | Add            | PC   | Extshft | Read             |           |                 | Dispatch 1 |

| Mem1     | Add            | Α    | Extend  |                  |           |                 | Dispatch 2 |

| LW2      |                |      |         |                  | Read ALU  |                 | Seq        |

|          |                |      |         | Write MDR        |           |                 | Fetch      |

| SW2      |                |      |         |                  | Write ALU |                 | Fetch      |

| Rformat1 | Func code      | Α    | В       |                  |           |                 | Seq        |

|          |                |      |         | Write ALU        |           |                 | Fetch      |

| BEQ1     | Subt           | Α    | В       |                  |           | ALUOut-cond     | Fetch      |

| JUMP1    |                |      |         |                  |           | Jump address    | Fetch      |

### Control Signals

| Field name       | Value        | Signals active | Comment                                                                  |

|------------------|--------------|----------------|--------------------------------------------------------------------------|

|                  | Add          | ALUOp = 00     | Cause the ALU to add.                                                    |

| ALU control      | Subt         | ALUOp = 01     | Cause the ALU to subtract; this implements the compare for               |

|                  |              |                | branches.                                                                |

|                  | Func code    | ALUOp = 10     | Use the instruction's function code to determine ALU control.            |

| SRC1             | PC           | ALUSrcA = 0    | Use the PC as the first ALU input.                                       |

|                  | A            | ALUSrcA = 1    | Register A is the first ALU input.                                       |

|                  | В            | ALUSrcB = 00   | Register B is the second ALU input.                                      |

| SRC2             | 4            | ALUSrcB = 01   | Use 4 as the second ALU input.                                           |

|                  | Extend       | ALUSrcB = 10   | Use output of the sign extension unit as the second ALU input.           |

|                  | Extshft      | ALUSrcB = 11   | Use the output of the shift-by-two unit as the second ALU input.         |

|                  | Read         |                | Read two registers using the rs and rt fields of the IR as the register  |

|                  |              |                | numbers and putting the data into registers A and B.                     |

|                  | Write ALU    | RegWrite,      | Write a register using the rd field of the IR as the register number and |

| Register         |              | RegDst = 1,    | the contents of the ALUOut as the data.                                  |

| control          |              | MemtoReg = 0   |                                                                          |

|                  | Write MDR    | RegWrite,      | Write a register using the rt field of the IR as the register number and |

|                  |              | RegDst = 0,    | the contents of the MDR as the data.                                     |

|                  |              | MemtoRea = 1   |                                                                          |

|                  | Read PC      | MemRead,       | Read memory using the PC as address; write result into IR (and           |

|                  |              | lorD = 0       | the MDR).                                                                |

| Memory           | Read ALU     | MemRead,       | Read memory using the ALUOut as address; write result into MDR.          |

|                  |              | lorD = 1       |                                                                          |

|                  | Write ALU    | MemWrite,      | Write memory using the ALUOut as address, contents of B as the           |

|                  |              | lorD = 1       | data.                                                                    |

|                  | ALU          | PCSource = 00  | Write the output of the ALU into the PC.                                 |

|                  |              | PCWrite        |                                                                          |

| PC write control | ALUOut-cond  | PCSource = 01, | If the Zero output of the ALU is active, write the PC with the contents  |

|                  |              | PCWriteCond    | of the register ALUOut.                                                  |

|                  | jump address | PCSource = 10, | Write the PC with the jump address from the instruction.                 |

|                  | · ·          | PCWrite        | · ·                                                                      |

|                  | Seq          | AddrCtl = 11   | Choose the next microinstruction sequentially.                           |

| Sequencing       | Fetch        | AddrCtl = 00   | Go to the first microinstruction to begin a new instruction.             |

|                  | Dispatch 1   | AddrCtl = 01   | Dispatch using the ROM 1.                                                |

|                  | Dispatch 2   | AddrCtl = 10   | Dispatch using the ROM 2.                                                |

#### The Controller

#### The Dispatch ROMs

| Dispatch ROM 1 |          |          |  |  |  |  |

|----------------|----------|----------|--|--|--|--|

| Op             | Value    |          |  |  |  |  |

| 000000         | R-format | Rformat1 |  |  |  |  |

| 000010         | jmp      | JUMP1    |  |  |  |  |

| 000100         | beq      | BEQ1     |  |  |  |  |

| 100011         | lw       | Mem1     |  |  |  |  |

| 101011         | SW       | Mem1     |  |  |  |  |

| Dispatch ROM2  |    |       |  |  |  |

|----------------|----|-------|--|--|--|

| Op Opcode name |    | Value |  |  |  |

| 100011         | lw | LW2   |  |  |  |

| 101011         | SW | SW2   |  |  |  |

Fig. C.5.2

Multicycle Design-56

Computer Architecture CTKing/TTHwang

#### Our Plan: Using ROM

Multicycle Design-57

Computer Architecture CTKing/TTHwang

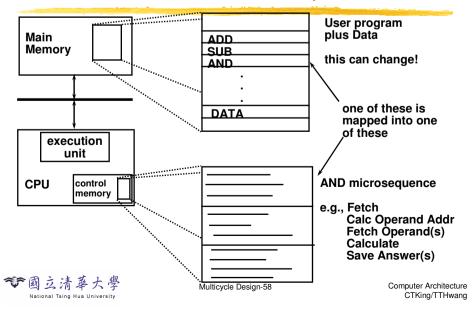

#### Microinstruction Interpretation

# Microprogramming Using ROM: Pros and Cons

- Ease of design

- Flexibility

- Each to adapt to changes in organization, timing, technology

- Can make changes late in design cycle, or even in the field

- Generality

- Implement multiple inst. sets on same machine

- Can tailor instruction set to application

- Can implement very powerful instruction sets (just more control memory)

- Compatibility

- Many organizations, same instruction set

- Costly to implement and Slow

Multicycle Design-59

Computer Architecture CTKing/TTHwang

#### 5) Microinstruction Encoding

| State number | Cor  | trol bits | 17- 2 | Control bits 1- 0 |

|--------------|------|-----------|-------|-------------------|

| 0            | 1001 | 0100000   | 01000 | 11                |

| 1            | 0000 | 0000000   | 11000 | 01                |

| 2            | 0000 | 0000000   | 10100 | 10                |

| 3            | 0011 | 0000000   | 00000 | 11                |

| 4            | 0000 | 0010000   | 00010 | 00                |

| 5            | 0010 | 1000000   | 00000 | 00                |

| 6            | 0000 | 0000010   | 00100 | 11                |

| 7            | 0000 | 0000000   | 00011 | 00                |

| 8            | 0100 | 0000101   | 00100 | 00                |

| 9            | 1000 | 0001000   | 00000 | 00                |

Fig. C.4.5

Bits 7-13 can be encoded to 3 bits because only one bit of the 7 bits of the control word is ever active

Multicycle Design-60

Computer Architecture . CTKing/TTHwang

#### Minimal vs. Maximal Encoding

- Minimal (Horizontal):

- + more control over the potential parallelism of operations in the datapath

- uses up lots of control store

- Maximal (Vertical):

- + uses less number of control store

- extra level of decoding may slow the machine down

Multicycle Design-61

Computer Architecture CTKing/TTHwang

#### Summary of Control

- Control is specified by a finite state diagram

- Specialized state-diagrams easily captured by microsequencer

- simple increment and "branch" fields

- datapath control fields

- Control can also be specified by microprogramming

- Control is more complicated with:

- complex instruction sets

- restricted datapaths

- Simple instruction set and powerful datapath => simple control

- could reduce hardware

- Or go for speed => many instructions at once!

#### **Outline**

- Designing a processor

- Building the datapath

- ♦ A single-cycle implementation

- A multicycle implementation

- Multicycle datapath

- Multicycle execution steps

- Multicycle control

- Microprogramming: simplifying control

- Exceptions

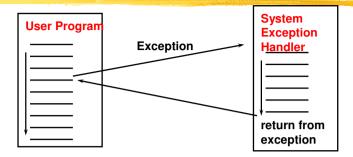

#### **Exceptions**

- Normal control flow: sequential, jumps, branches, calls, returns

- Exception = unprogrammed control transfer

- system takes action to handle the exception

- must record address of the offending instruction

- should know cause and transfer to proper handler

- if returns to user, must save & restore user state

Multicycle Design-64

Computer Architecture CTKing/TTHwang

Computer Architecture

. CTKing/TTHwang

#### User/System Modes

- By providing two modes of execution (user/system), computer may manage itself

- OS is a special program that runs in the privileged system mode and has access to all of the resources of the computer

- Presents "virtual resources" to each user that are more convenient than the physical resources

- files vs. disk sectors

- virtual memory vs. physical memory

- protects each user program from others

- Exceptions allow the system to taken action in response to events that occur while user program is executing

- OS begins at the handler

Multicycle Design-65

Computer Architecture CTKing/TTHwang

#### Two Types of Exceptions

- Interrupts:

- caused by external events and asynchronous to execution

- => may be handled between instructions

- simply suspend and resume user program

- Exceptions:

- caused by internal events and synchronous to execution, e.g., exceptional conditions (overflow), errors (parity), faults

- instruction may be retried or simulated and program continued or program may be aborted

#### MIPS Convention of Exceptions

- MIPS convention:

- exception means any unexpected change in control flow, without distinguishing internal or external

- use interrupt only when the event is externally caused

| Type of event               | From where? | MIPS terminology |

|-----------------------------|-------------|------------------|

| I/O device request          | External    | Interrupt        |

| Invoke OS from user program | Internal    | Exception        |

| Hardware malfunctions       | Either      | Exception or     |

|                             |             | Interrupt        |

| Arithmetic overflow         | Internal    | Exception        |

| Using an undefined inst.    | Internal    | Exception        |

|                             |             | •                |

#### Precise Interrupts

- Precise: machine state is preserved as if program executed upto the offending inst.

- Same system code will work on different implementations of the architecture

- Position clearly established by IBM, and taken by MIPS

- Difficult in the presence of pipelining, out-ot-order execution....

- Imprecise: system software has to figure out what is where and put it all back together

- Performance goals often lead designers to forsake precise interrupts

- system software developers, user, markets etc., usually wish they had not done this

Multicycle Design-68

Computer Architecture . CTKing/TTHwang

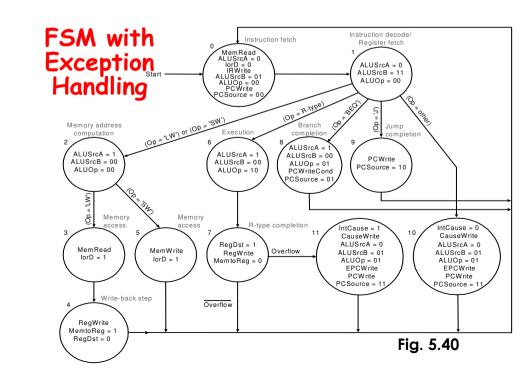

#### Handling Exceptions in Our Design

- Consider two types of exceptions: undefined instruction & arithmetic overflow

- Basic actions on exception:

- Save state: save the address of the offending instruction in the exception program counter (EPC)

- Transfer control to OS at some specified address => need to know the cause for the exception => then know the address of exception handler

- After service, OS can terminate the program or continue its execution, using EPC to return

Multicycle Design-69

Computer Architecture CTKing/TTHwang

#### Saving State: General Approaches

- Push it onto the stack

- Vax, 68k, 80x86

- Save it in special registers

- MIPS EPC. BadVaddr. Status. Cause

- Shadow Registers

- M88k

National Tsing Hua University

Save state in a shadow of the internal pipeline registers

### Addressing the Exception Handler

Multicycle Design-71

Traditional approach: interrupt vector

• The cause of exception is a vector giving the address of the handler

PC <- MEM[ IV\_base + cause | | 00]</li>

• 68000, Vax, 80x86, . . .

iv base

handlei code cause

> handle entry co

cause

- RISC Handler Table

- PC <- IV base + cause | | 0000</li>

- Saves state and jumps

- Sparc, PA, M88K, . . .

- MIPS approach: fixed entry

- use a status register (cause register) to hold a field to indicate the cause

- PC <- EXC addr</li>

iv base

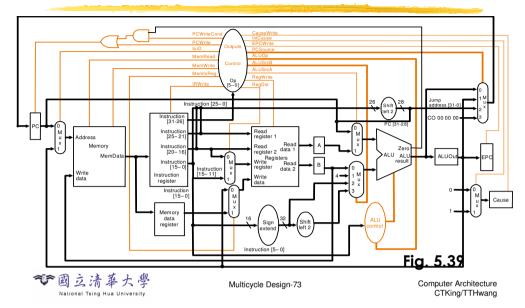

#### Additions for Our Design

- EPC: reg. to hold address of affected inst.

- Cause: reg. to record cause of exception

- Assume LSB encodes the two possible exception sources: undefined instruction=0 and arithmetic overflow=1

- Two control signals to write EPC (EPCWrite) and Cause (CauseWrite), and one control signal (IntCause) to set LSB of Cause register

- Be able to write exception address into PC, assuming at C000 0000<sub>hex</sub>

- => needs a 4-way MUX to PC

- May undo PC = PC + 4, since want EPC to point to offending inst. (not its successor)

Multicycle Design-72

Computer Architecture CTKing/TTHwang

### Datapath with Exception Handling

### **Exception Detection**

- Undefined instruction: detected when no next state is defined from state 1 for the op value

- Handle this by defining the next state value for all op values other than lw, sw, 0 (R-type), jmp, and beq as a new state, "other"

- Arithmetic overflow: detected with the Overflow signal out of the ALU

- This signal is used in the modified FSM to specify an additional possible next state

Note: challenge in designing control of a real machine is to handle different interactions between instructions and other exception-causing events such that control logic remains small and fast

Complex interactions makes the control unit the most challenging aspect of hardware design

Computer Architecture CTKing/TTHwang

#### Summary

- Specialize state diagrams easily captured by microsequencer

- simple increment and branch fields

- datapath control fields

- Control design reduces to microprogramming

- Exceptions are the hard part of control

- Need to find convenient place to detect exceptions and to branch to state or microinstruction that saves PC and invokes OS

- Harder with pipelined CPUs that support page faults on memory accesses, i.e., the instruction cannot complete AND you must restart program at exactly the instruction with the exception

Multicycle Design-76

Computer Architecture CTKing/TTHwang